コース概要

このコースは、コニカミノルタ株式会社作成のデジタル回路設計者育成トレーニングに基づき提供いたします。

本コースは、Artix-735T Arty Artix-7FPGA 評価キットとLCDシールドボードを使用し、LCD制御回路の

開発・実際に動作させることを通して、FPGAをターゲットとしたLSI設計手法の基本を習得できます。

※本コースは、演習用PCをご準備頂く必要があります。

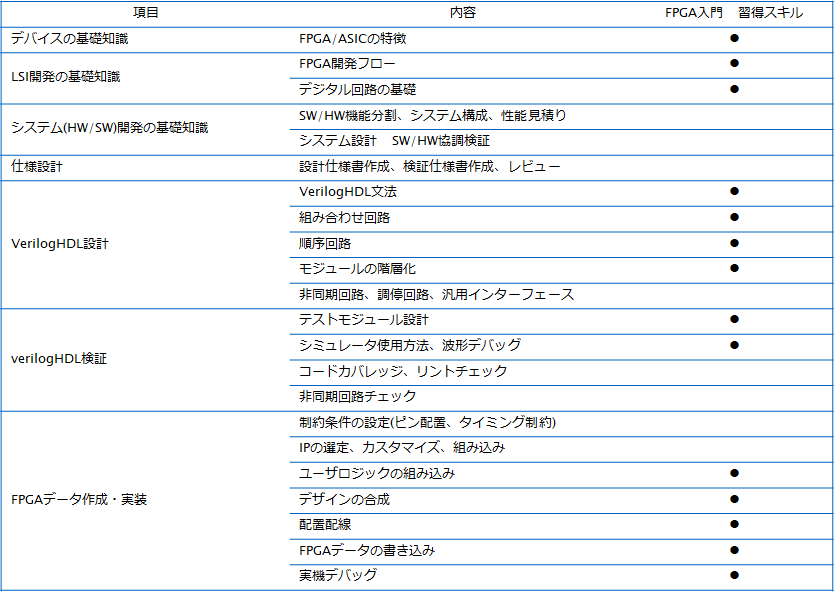

本コースにおける習得スキル

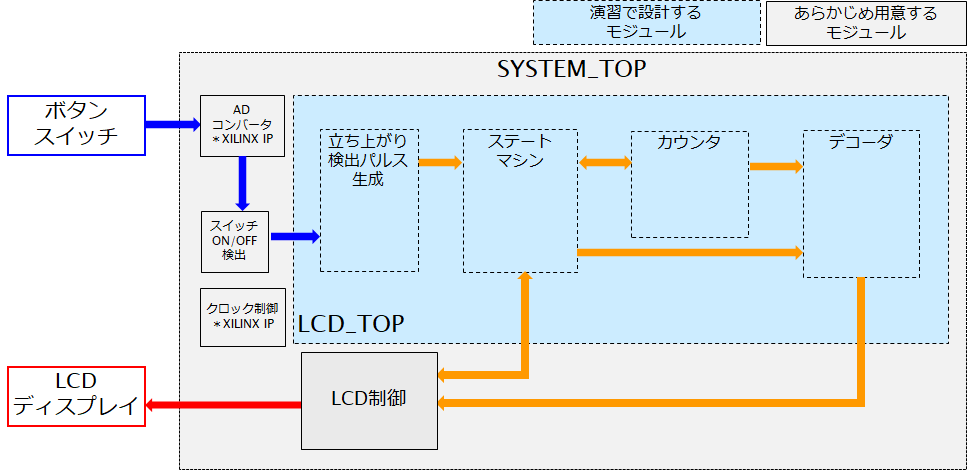

FPGAで動作させる回路の全体構成

会場

オンライン開催

1. 配信について

・遠隔会議システムのCisco Webex Meetingを使用します。

・受講者には指定のメールアドレスにWebex Meetingの招待を送付します。

・接続場所は制限しませんが、お申込者の方のみの受講となります(複数での受講は不可)

2. 事前準備について

・接続トライアルの機会をご用意します。詳細については、お申込み受付後ご案内します。

・通信の安定している環境でご利用ください。また、通信量に上限のない回線をご利用ください。

・音声が聞ける状態のPCやタブレット等をご準備ください。

・周囲に迷惑の掛からない場所を確保してください。

・使用方法について、簡易マニュアルを用意しております。(こちらをクリック)

コース詳細

| コンテンツ提供 | コニカミノルタ株式会社 |

| 講師 | 株式会社エッチ・ディー・ラボ |

| ソフトウェアツール | Vivado Design Suite 2018.3 以降 |

| ハードウェア | Artix-735T Arty Artix-7FPGA 評価キット及びLCDシールドボード |

| トレーニング期間 | 2日間 |

| 受講料 | 98,000円(税抜) ※ボード付き特別価格 |

| 受講対象者 | デジタル回路設計・FPGA設計に興味のある方 未経験者/初級者向け |

| 受講要件 |

演習用PC(Vivado Design Suite)をご準備頂くこと ※バージョンについては調整中です。 |

| コース内容 |

【講義】 1. はじめに 1.1 アジェンダ 1.2 本講座における習得スキル 1.3 講座のねらい・特徴 2. デバイスの基礎知識 3 FPGA(LSI)開発フロー 4 デジタル回路 5. Verilog HDL -設計編- 6. Verilog HDL -検証編- 7. Verilog HDL まとめ 8. 論理シミュレーション(Vivado Simulator) 9. FPGA データ作成・実装(Vivado Design Suite) 【演習問題】 |

演習用PCの要件

■OS: Windows 10.0 1803 Update, 10.0 1809 Update (64 ビッ ト 英語版 日本語版)

■推奨メモリ:8Gb以上

■推奨CPU: Core i7

■推奨されるHDDディスク容量: 100GB 以上の空きスペース

⇒以下を含みます

・ツールインストール後の容量

・ツールインストーラー自身

・ツールインストール時の展開領域

■Vivado Design Suite 2018.3をインストール済みであること

ツールのインストール

Vivado Design Suite 2018.3 以降をご準備ください。

ダウンロードページはこちらをクリックしてください

※XILINX社へのユーザー登録が必要です。

■WebPACKライセンスの取得、インストール済みであること

■PCのシステム要件およびインストールの詳細について

■Vivadoの使用方法について

Vivadoを初めて使用する方、使用経験が少ない方は事前に以下の資料をご覧ください。

- Vivado Design Suite チュートリアル デザイン フローの概要 2018.3

- Vivado デザイン フローの概要 (日本語吹替)Vivado デザイン フローの概要 (日本語吹替)

※題名をクリックすると、いずれもXILINX社のページが開きます。

チラシ

準備中