※開催についてのお問い合わせ先:training-qa@hdlab.com までメールでご連絡ください。

※ツールのインストールの情報を追記しました。

コース概要

講 師:小野 雅晃 様(FPGAの部屋主宰)

講座内容:

・Zynqデバイスの概要

・AXI4インターフェースの概要

・Vitis HLSの基礎的な使い方

演習内容:

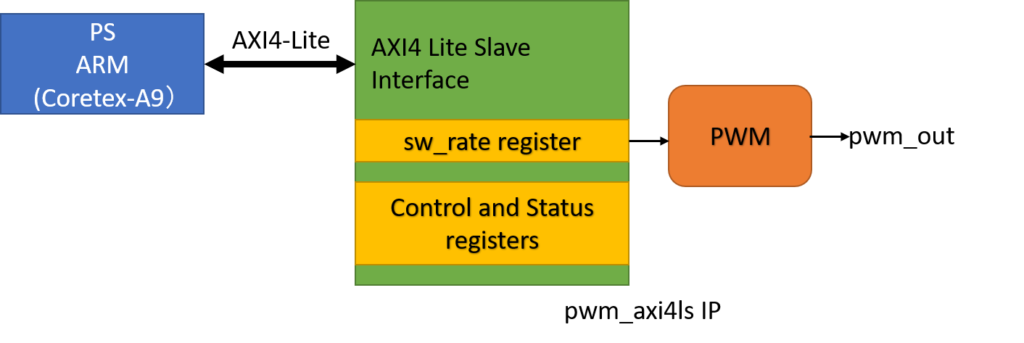

・AXI4 Lite Slaveインターフェースの作成

・AXI4 Masterインターフェースの作成

・AXI4 Streamインターフェースの作成

全て講師と共に実装し実機確認を行います。

作成する回路の構成:

会場

対象者

- VivadoのIPインテグレータでAXIを構成する予定の方

- HLSを使ってみたい方

- 初めてHLSによる高位合成に取り組むデジタル回路技術者

※HLSの操作は、講師とともに一緒に行います。

[受講要件]

FPGA(特にZynqシリーズ)の基本的な知識があること。

HDL,C/C++言語の基礎知識のあること。

演習用PC(指定のツールをインストール済み)をご準備頂くこと。

※Vivado知識がある事が望ましい

コース詳細

| コンテンツ提供 | 小野 雅晃様 |

| 講師 | 小野 雅晃様 |

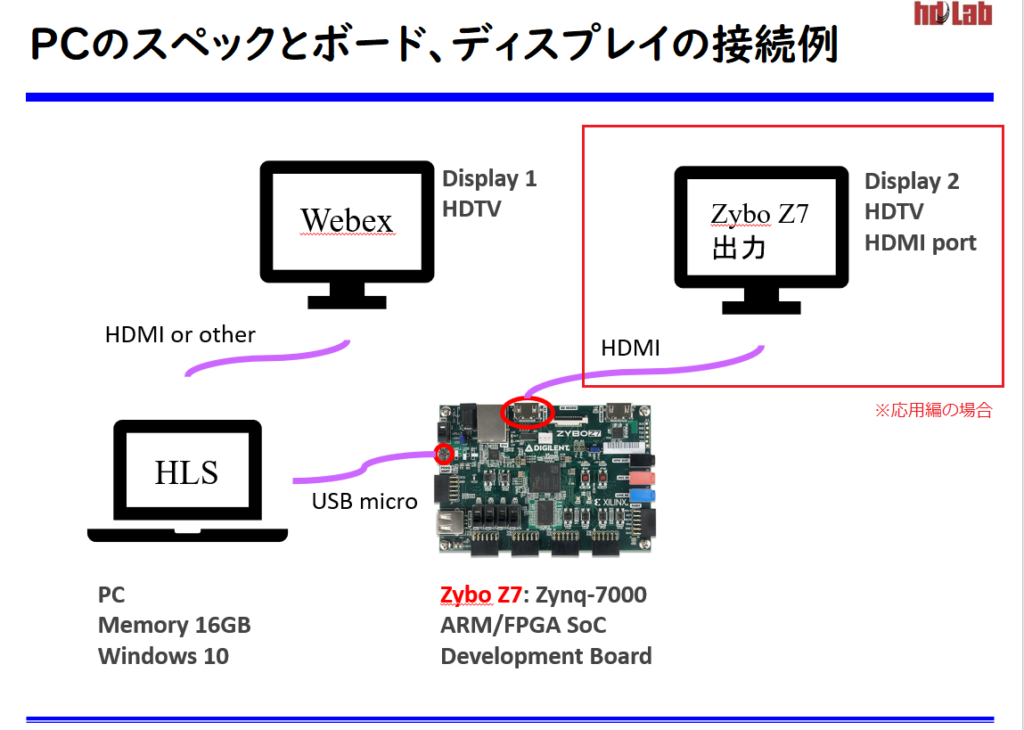

| ソフトウェアツール | Vitis 2021.1 Vitis HLS2 2021.1, Vivado 2021.1 ※ツール版数は変更になる場合がございます。 |

| ハードウェア | Zynqボード(Zybo Z7-10またはZ7-20) 受講の際は、Zybo Z7-10またはZ7-20をご持参ください。 |

| トレーニング期間 | 2日間 |

| 受講料 | 107,800円(税抜 98,000円) |

| 受講対象者 | Zynq SoCを使ってみたい方 VivadoのIPインテグレータでAXIを構成する予定の方 HLSを使ってみたい方 初めてHLSによる高位合成に取り組むデジタル回路技術者 ※HLSの操作は、講師とともに一緒に行います。 |

| 受講要件 |

FPGA(特にZynqシリーズ)の基本的な知識があること。 HDL,C/C++言語の基礎知識のあること。 演習用PC(指定のツールをインストール済み)をご準備頂くこと。 ※Vivado知識がある事が望ましい |

| コース内容 |

【1日目】 午前 1. Zynqデバイスの説明 2. VivadoでZynqを実装しながら構成を説明(ハンズオン) 3. VivadoでZynq+GPIOを実装し、VitisでLチカアプリケーションを作成(ハンズオン) 午後 【2日目】 午後 |

演習用PCの要件等

ツールのインストール

チラシ

準備中