■トレーニングイベント概要

準備中

■トレーニングイベント開催概要

- タイトル:Embedded Heterogeneous Design

- 日時:2026年3月19日(木)10:00 ~17:00

- 費用:無償

- 内容:講義&デモ

- 講師:平郡 政幸氏(エッチディーラボ契約講師:エムシップ・デザインズ合同会社)

- 開催方式:オンライン(WebEx Meeting)

- ご登録(お申込み)ページ: 下記ボタンをクリックしてください。(3/18 17:00 締切)

■お問合せ先

training-qa@hdlab.co.jp 宛にお願いします。

Designing with the Versal Adaptive SoC: Quick Start 2025.1

■トレーニングイベント概要

プログラマブル ネットワーク オン チップ (NoC) と AI エンジンを搭載した AMD Versal™ アダプティブ SoC ヘテロジニアス

アーキテクチャと、Versal デバイスをターゲットとするさまざまなデザイン ツール フローの使用方法を学びます。

組み込みソフトウェア開発とアプリケーションのパーティショニングに関する知識を習得します。

このコースの重点は次のとおりです。

・AMD Versal Adaptive SoC:概要

・アーキテクチャ

・デザイン ツール フロー

・エンベデッド ソフトウエア開発

・NoCの紹介と概念

・AI エンジン

注意!

配付するテキストは一部の章に限定しております。

過去のイベントでご提供した無料再配信はございません。

本イベントはオンライン・オンデマンドで開催する同タイトルの講座の短縮版です。

※有償講座の開催日程・詳細は、「こちら」をクリックしてください。

■トレーニングイベント開催概要

- タイトル:Designing with the Versal Adaptive SoC: Quick Start 2025.1

- 日時:2025年12月24日(水)10:00 ~17:00

- 費用:無償

- 内容:講義&デモ

- 講師:平郡 政幸氏(エッチディーラボ契約講師:エムシップ・デザインズ合同会社)

- 開催方式:オンライン(WebEx Meeting)

- ご登録(お申込み)ページ: 受付終了

今回のイベントは、Webex Meeting の登録機能により、ご登録いただきます。

1. イベント用のWebex Meeting登録ページを開く

2. 必要事項を入力し、登録する

3. 承認・招待状メールの到着を待つ(承認は、五営業日以内に行います)

ご登録の詳細については、

「Webex Meetingでの登録について」をご覧ください。

■トレーニングイベント詳細(タイムテーブル)

| タイトル | 時間 |

| 1 | ご案内 | 10:00-10:10 |

| 2 | AMD Versal Adaptive SoC:概要 | 10:10 |

| 3 | アーキテクチャ | |

| 昼休み | 11:50-13:20 |

| 4 | デザイン ツール フロー | |

| 5 | デザイン ツール フロー | |

| 休憩 | 14:50-15:20 |

| 6 | エンベデッド ソフトウエア開発 | |

| 7 | NoCの紹介と概念 | |

| 8 | AI エンジン | |

※ 開始前に接続テストの時間を設ける予定です。(09:00~10:00の間)

■お問合せ先

training-qa@hdlab.co.jp 宛にお願いします。

Designing with Versal AI Edge Series Gen 2:

AIE-ML v2 Architecture and Design Flow 2025.1

■トレーニングイベント概要

本イベントでは、AMDのVersal™ AI Edge Series Gen 2デバイスに搭載された**AI Engine ML v2 (AIE-ML v2)**の

アーキテクチャと設計フローについて説明します。

AIエンジンの進化点、プログラミングモデル、Vitisツールを使った開発・解析方法を体系的に説明します。

次の点に重点を置きます。

- 新しいAIE-ML v2アーキテクチャの概要と前世代(AIE, AIE-ML)との比較

- システム設計計画とアプリケーション分割手法(異なる演算ドメインの活用)

- VitisツールフローによるAI Engine設計・実装・性能解析

- ネイティブおよびサポートされるデータ型�(SIMD命令、浮動小数点/ブロック浮動小数点対応)

- **メモリタイル(共有バッファ)**の使用とプログラミングモデル

- AI Engine DSPライブラリによるマルチタイル行列演算の実装

- Vitis Analyzerを用いたスループット・性能解析と最適化方法

■トレーニングイベント開催概要

- タイトル:Designing with Versal AI Edge Series Gen 2: AIE-ML v2 Architecture and Design Flow 2025.1

- 日時:2025年12月19日(金)10:00 ~17:00

- 費用:無償

- 内容:講義&デモ

- 講師:平郡 政幸氏(エッチディーラボ契約講師:エムシップ・デザインズ合同会社)

- 開催方式:オンライン(WebEx Meeting)

- ご登録(お申込み)ページ: 受付終了

■トレーニングイベント詳細(タイムテーブル)

| タイトル | 時間 |

| 1 | ご案内 | 10:00-10:10 |

| 2 | AMD Versal アダプティブ SoC: アーキテクチャの概要 | 10:10-10:50 |

| 3 | AIE-ML v2 アーキテクチャの概要 | 10:50-11:50 |

| 昼休み | 11:50-13:20 |

| 4 | AMD Versal AI エッジ シリーズ Gen 2: AIE-ML v2 ツール フロー | 13:20-14:50 |

| 休憩 | 14:50-15:20 |

| 5 | <デモ> AIE-ML v2 ツール フロー | 15:20-17:00 |

※ 上記以外に1時間に10分程度休憩を取ります。

※ タイムテーブルは検討中のものです。内容は予告なく変更する場合がございますので、ご了承ください。

※ 開始前に接続テストの時間を設ける予定です。(09:00~10:00の間)

■お問合せ先

training-qa@hdlab.co.jp 宛にお願いします。

Designing with the Versal AI Edge Series Gen 2

and Prime Series Gen 2: Architecture 2025.1

■トレーニングイベント概要

本イベントでは、AMDのVersal™ AI Edge Series Gen 2およびPrime Series Gen 2アダプティブSoCのアーキテクチャを1日に短縮して説明します。

プログラマブルロジック、次世代AIエンジン、高性能プロセッシングシステム(PS)を統合したSoC設計の理解を目的に概要を説明します。

次の点に重点を置きます。

- VersalアダプティブSoC内の計算リソースの構成

- 高性能プロセッシングシステム(Arm Cortex-A78AE / R52)の詳細

- 次世代AI Engine(AIE-ML v2)アーキテクチャ

- ネットワーク・オン・チップ(NoC)の構造

- DDR5 / LPDDR5Xメモリコントローラ

- 新しい画像・映像処理ハードブロック(VCU2, GPU, ISP)

- 機能安全(Functional Safety)とセキュリティ強化

- PCI Express Gen5および32G高速シリアルトランシーバ

■トレーニングイベント開催概要

- タイトル:Designing with the Versal AI Edge Series Gen 2 and Prime Series Gen 2: Architecture 2025.1

- 日時:2025年11月28日(金)10:00 ~17:00

- 費用:無償

- 内容:講義&デモ

- 講師:平郡 政幸氏(エッチディーラボ契約講師:エムシップ・デザインズ合同会社)

- 開催方式:オンライン(WebEx Meeting)

- ご登録(お申込み)ページ: 受付終了

今回のイベントは、Webex Meeting の登録機能により、ご登録いただきます。

1. イベント用のWebex Meeting登録ページを開く

2. 必要事項を入力し、登録する

3. 承認・招待状メールの到着を待つ(承認は、五営業日以内に行います)

ご登録の詳細については、

「Webex Meetingでの登録について」をご覧ください。

■トレーニングイベント詳細(タイムテーブル)

| タイトル | 時間 |

| 1 | ご案内 | 10:00-10:10 |

| 2 | Versalの紹介とポートフォリオの概要 | 10:10-10:40 |

| 3 | アーキテクチャの概要 | 10:50-11:50 |

| 昼休み | 11:50-13:20 |

| 4 | プロセッシング システム | 13:20-13:50 |

| 5 | AIE-ML v2 アーキテクチャの概要 | 13:50-14:20 |

| 6 | <デモ>AIE-ML v2 アーキテクチャの概要 | 14:20-14:50 |

| 休憩 | 14:50-15:20 |

| 7 | DDR5を使った設計 | 15:20-15:50 |

| 8 | PCI Expressソリューション | 15:50-16:20 |

| 9 | <デモ>PCI Expressソリューション | 16:20-16:50 |

※ 開始前に接続テストの時間を設ける予定です。(09:00~10:00の間)

■お問合せ先

training-qa@hdlab.co.jp 宛にお願いします。

New features and enhancements

in AMD Vitis Unified Software Platform

2025.1 Release

■トレーニングイベント概要

本イベントでは、バージョン2025.1よりEclipse Theia ベース GUI となったAMD Vitis™ Unified IDE に

ついて、最新版の2025.1 を使用した組み込みソフトウェアの設計と開発に必要なツールとテクニックを説明します。

このコースでは次の点に重点を置きます。

・組み込みソフトウェア開発フローの基本を復習

・ Vitis Unified IDE の用語と機能の確認

・ベアメタルおよび Linux® アプリケーションの開発

・Vitis Unified IDE を使用したアプリケーションのデバッグ

・Vitis Python™ コマンド ライン インターフェイスの使用

・クラシック Vitis IDE から Vitis Unified IDE への移行

注意!過去のイベントでご提供した無料再配信はございません。

■トレーニングイベント開催概要

- タイトル:New features and enhancements in AMD Vitis Unified Software Platform 2025.1

- 日時:2025年9月26日(金)10:00 ~17:00

- 費用:無償

- 内容:講義&デモ

- 講師:平郡 政幸氏(エッチディーラボ契約講師:エムシップ・デザインズ合同会社)

- 開催方式:オンライン(WebEx Meeting)

- ご登録(お申込み)ページ:9/25 17:00 締め切りました

■トレーニングイベント詳細(タイムテーブル)

| タイトル | 時間 |

| 1 | ご案内 | 10:00-10:10 |

| 2 | AMD Vitis ソフトウェア プラットフォーム 2025.1 リリースのハイライト | 10:10-10:40 |

| 3 | AMD Versal AI Edge/Prime Series Gen 2: アーキテクチャの概要 | 10:50-11:50 |

| 昼休み | 11:50-13:20 |

| 4 | AMD Vitis Unified IDE の活用 | 13:20-13:50 |

| 5 | <デモ> AMD Vitis Unified IDE の活用 | 13:50-14:20 |

| 6 | AMD Vitis Unified IDE を使用したデバッグ | 14:20-14:50 |

| 休憩 | 14:50-15:20 |

| 7 | Vitis コマンド ライン インターフェイスからの Python コマンドの使用 | 15:20-15:50 |

| 8 | AMD Vitis Unified IDE への移行 | 15:50-16:20 |

| 9 | <デモ>AMD Vitis Unified IDE への移行 | 16:20-16:50 |

※ 上記以外に1時間に10分程度休憩を取ります。

※ タイムテーブルは検討中のものです。内容は予告なく変更する場合がございますので、ご了承ください。

※ 開始前に接続テストの時間を設ける予定です。(09:00~10:00の間)

■お問合せ先

training-qa@hdlab.co.jp 宛にお願いします。

Migrating from UltraScale+ Devices to Versal Adaptive SoCs 2024.1

■トレーニングイベント概要

このコースでは、AMD UltraScale+ デバイスから AMD Versal アダプティブ SoC に既存の設計を効率的に移行するためのさまざまなアプローチについて説明します。

また、システム設計の計画とパーティショニングの方法論、およびさまざまなシステム設計タイプの設計移行に関する考慮事項についても説明します。

このコースの重点は次のとおりです。

- Versal アダプティブ SoC のさまざまな機能ブロックを識別して、前世代の UltraScale+ デバイスのブロックと比較する

- すべての開発者向けの開発プラットフォームについて説明する

- 既存の設計を Versal アダプティブ SoC に移行するアプローチを確認する

- システム設計タイプに基づいてシステム設計移行を計画するための推奨方法を指定する

- AI エンジン システムのパーティショニング計画について説明する

- PL のみの設計と Zynq UltraScale+ MPSoC 設計の設計移行に関する考慮事項を特定する

- Zynq UltraScale+ MPSoC ベースのシステムレベル設計を Versal アダプティブ SoC に移行する

- Versal デバイスのハードウェア デバッグ機能の詳細を説明する

■トレーニングイベント開催概要

-

- タイトル:Migrating from UltraScale+ Devices to Versal Adaptive SoCs 2024.1

- 日時:2025年2月18日(火)10:00 ~17:00

- 費用:無償

- 内容:講義&デモ

- 講師:平郡 政幸氏(エッチディーラボ契約講師:エムシップ・デザインズ合同会社)

- 開催方式:オンライン(WebEx Meeting)

- ご登録締め切り: 2025年2月17日(月)午後5時

- ご登録(お申込み)ページ:締切りました。

今回のイベントは、Webex Meeting の登録機能により、ご登録いただきます。

1. イベント用のWebex Meeting登録ページを開く

2. 必要事項を入力し、登録する

3. 承認・招待状メールの到着を待つ(承認は、五営業日以内に行います)

ご登録の詳細については、「Webex Meetingでの登録について」をご覧ください。

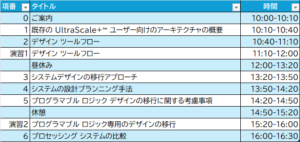

■トレーニングイベント詳細(タイムテーブル)

※ 開始前に接続テストの時間を設ける予定です。(9:00~10:00の間)

■お問合せ先

training-qa@hdlab.co.jp 宛にお願いします。

【開催終了】AMD Versal Adaptive SoCクイックスタート

~ Designing with AMD Versal Adaptive SoC: Quick Start

■トレーニングイベント概要

プログラマブル ネットワーク オン チップ (NoC) と AI エンジンを搭載した AMD Versal™ アダプティブ SoC ヘテロジニアス

アーキテクチャと、Versal デバイスをターゲットとするさまざまなデザイン ツール フローの使用方法を学びます。

組み込みソフトウェア開発とアプリケーションのパーティショニングに関する知識を習得します。

また、Versal アーキテクチャへのシステム移行の実行方法も学習します。

このコースの重点は次のとおりです。

・Versal アダプティブ SoC のアーキテクチャの確認

・Versal アーキテクチャで使用可能なさまざまなエンジンと、エンジンに含まれるリソースの説明

・Versal デバイスのエンベデッド ソフトウェア開発フローのデモ

・ネットワークオンチップ(NoC)とAIエンジンのアーキテクチャの説明

・計算モデルに基づくアプリケーションの分割の説明

・Versal デバイスのさまざまな機能ブロックと前世代デバイスの比較

注意!過去のイベントでご提供した無料再配信はございません。

本イベントは8月9月よりオンライン・オンデマンドで開催するする同タイトルの講座の短縮版です。

※有償講座の開催日程・詳細は、「こちら」をクリックしてください。

■トレーニングイベント開催概要

- タイトル:AMD Versal Adaptive SoCクイックスタート ~ Designing with AMD Versal Adaptive SoC: Quick Start Start

- 日時:2024年7月18日(木)10:00 ~17:00

- 費用:無償

- 内容:講義&デモ

- 講師:平郡 政幸氏(エッチディーラボ契約講師:エムシップ・デザインズ合同会社)

- 開催方式:オンライン(WebEx Meeting)

今回のイベントは、Webex Meeting の登録機能により、ご登録いただきます。

1. イベント用のWebex Meeting登録ページを開く

2. 必要事項を入力し、登録する

3. 承認・招待状メールの到着を待つ(承認は、五営業日以内に行います)

ご登録の詳細については、「Webex Meetingでの登録について」をご覧ください。

■トレーニングイベント詳細(タイムテーブル)

| タイトル |

時間 |

| 開講 |

10:00-10:05 |

| 1. AMD Versal Adaptive SoC:概要 |

10:05~ |

| 2. アーキテクチャ |

~10:45 |

| BRAKE |

10:45~11:00 |

| 3. デザイン ツール フロー |

11:00~12:00 |

| LUNCH |

12:00~13:30 |

| 4. エンベデッド ソフトウエア開発 |

13:30~ |

| 5. NoCの紹介と概念 |

~15:15 |

| BRAKE |

15:15~15:30 |

| 6. アプリケーションのパーティショニング |

15:30~ |

| LAB1 demo(QEMU) |

~17:00 |

※ 上記以外に1時間に10分程度休憩を取ります。

※ タイムテーブルは検討中のものです。内容は予告なく変更する場合がございますので、ご了承ください。

※ 開始前に接続テストの時間を設ける予定です。(9:00~10:00の間)

■お問合せ先

training-qa@hdlab.co.jp 宛にお願いします。

New features and enhancements

in AMD Vitis Unified Software Platform

2023.2 Release

■トレーニングイベント概要

本イベントでは、バージョン2023.2よりEclipse Theia ベース GUI となったAMD Vitis™ Unified IDE を

使用した組み込みソフトウェアの設計と開発に必要なツールとテクニックを説明します。

このコースでは次の点に重点を置きます。

・組み込みソフトウェア開発フローの基本を復習

・ Vitis Unified IDE の用語と機能の確認

・ベアメタルおよび Linux® アプリケーションの開発

・Vitis Unified IDE を使用したアプリケーションのデバッグ

・Vitis Python™ コマンド ライン インターフェイスの使用

・クラシック Vitis IDE から Vitis Unified IDE への移行

注意!過去のイベントでご提供した無料再配信はございません。

■トレーニングイベント開催概要

- タイトル:New features and enhancements in AMD Vitis Unified Software Platform 2023.2

- 日時:2024年4月12日(金)10:00 ~17:00

- 費用:無償

- 内容:講義&デモ

- 講師:平郡 政幸氏(エッチディーラボ契約講師:エムシップ・デザインズ合同会社)

- 開催方式:オンライン(WebEx Meeting)

- ご登録(お申込み)ページ: 受付終了

今回のイベントは、Webex Meeting の登録機能により、ご登録いただきます。

1. イベント用のWebex Meeting登録ページを開く

2. 必要事項を入力し、登録する

3. 承認・招待状メールの到着を待つ(承認は、五営業日以内に行います)

ご登録の詳細については、「Webex Meetingでの登録について」をご覧ください。

■トレーニングイベント詳細(タイムテーブル)

| タイトル |

時間 |

| 開講 |

10:00-10:10 |

| 1. Overview of Embedded Software Development |

10:10~ |

| 2. Driving the AMD Vitis Unified IDE |

~12:00 |

| お昼休み |

12:00~13:30 |

| LAB1 demo(ZCU104) |

13:30~ |

| 3. Bare-metal Application Development |

|

| 4. Linux Software Application Development |

~15:00 |

| COFFEE BRAKE |

15:00~15:30 |

| 5. Debugging Using the AMD Vitis Unified IDE |

15:30~ |

| 6. Using Python Commands from the Vitis Command Line Interface |

|

| 7. Migrating to the AMD Vitis Unified IDE |

~17:00 |

※ 上記以外に1時間に10分程度休憩を取ります。

※ タイムテーブルは検討中のものです。内容は予告なく変更する場合がございますので、ご了承ください。

※ 開始前に接続テストの時間を設ける予定です。(10:00~12:00の間)

■お問合せ先

training-qa@hdlab.co.jp 宛にお願いします。