VITISでのエンベデッドシステムソフトウェア開発

| カテゴリ | Courseへのリンク | 日程 | 会場、受講料 | 状況 | category | 開催月 | 締切時間 | Flag |

|---|---|---|---|---|---|---|---|---|

| embe.png | Zynq UltraScale+ MPSoC VCU を使ったマルチメディアソリューション | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 1 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC システムアーキテクチャ | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 2 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| Vivado.png | PCI Express デザイン | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 3 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC: Quick Start | 随時 | オンデマンド TC:6TC 現金:¥66,000 | 4 | Versal Adaptive SoC | オンデマンド | 203510311700 | 1 |

| lang.png | Verification with SystemVerilog | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 受付停止 | HDL言語と検証 | オンデマンド | 203510311700 | 1 |

| lang.png | Designing with SystemVerilog | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 受付停止 | HDL言語と検証 | オンデマンド | 203510311700 | 1 |

| eembe.png | Vitis HLSを使った高位合成 | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 7 | SoCとVitisツール | オンデマンド | 203510311700 | 1 |

| embe.png | Kria KV260 Vision AI | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 8 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 9 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| Vivado.png | Vivado Design Suite でのUltraFast設計手法 | 7月1日(火) 申込締切日:6/20 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2052 | FPGAとVivadoツール | 2025年7月 | 202506201700 | 1 |

| Vivado.png | Vivado Design Suite でのインプリメント手法 | 7月3日(木) 申込締切日:6/24 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2054 | FPGAとVivadoツール | 2025年7月 | 202506241700 | 1 |

| eembe.png | Vitis HLSを使った高位合成 | 7月8日(火)-9日(水) 申込締切日:6/27 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2056 | SoCとVitisツール | 2025年7月 | 202506271700 | 1 |

| eembe.png | Zynq SoC システムアーキテクチャ | 7月10日(木)-11日(金) 申込締切日:7/1 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2057 | SoCとVitisツール | 2025年7月 | 202507011700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC Boot and Platform Management | 7月15日(火)-16日(水) 申込締切日:7/4 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 開催中止 | MPSoC/SoM | 2025年7月 | 202507041700 | 0 |

| embe.png | OS and Hypervisors in Adaptive SoCs | 7月17日(木)-18日(金) 申込締切日:7/8 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 開催中止 | MPSoC/SoM | 2025年7月 | 202507081700 | 0 |

| lang.png | [Verilog] Xilinx/Vivadoツールを使ったRTL設計初級 | 7月17日(木)-18日(金) 申込締切日:7/8 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2060 | HDL言語と検証 | 2025年7月 | 202507081700 | 1 |

| lang.png | FPGA向けRTL設計スタイルガイドセミナー | 7月22日(火)-23日(水) 申込締切日:7/10 10:00~18:00 | 新横浜(hdLab) TC:8TC 現金:¥107,800 | 2061 | HDL言語と検証 | 2025年7月 | 202507101700 | 1 |

| eembe.png | Embedded Linux Development Using Yocto | 7月18日(金) 申込締切日:7/9 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 開催中止 | SoCとVitisツール | 2025年7月 | 202507091700 | 0 |

| embe.png | Zynq UltraScale+ MPSoC システムアーキテクチャ | 7月23日(水)-24日(木) 申込締切日:7/11 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | MPSoC/SoM | 2025年7月 | 202507111700 | 0 |

| Vivado.png | Vivado Design Suite を使用したArtix-7 FPGA設計・開発入門 | 7月24日(木) 申込締切日:7/14 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2063 | FPGAとVivadoツール | 2025年7月 | 202507141700 | 1 |

| eembe.png | Migrating to the Vitis Unified IDE | 7月25日(金) 申込締切日:7/15 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2064 | SoCとVitisツール | 2025年7月 | 202507151700 | 1 |

| embe.png | Kria KV260 入門 | 8月1日(金) 申込締切日:7/23 13:00~18:00 | 新横浜(hdLab) TC:8TC 現金:TCのみ | 満席 | MPSoC/SoM | 2025年8月 | 202507231700 | 1 |

| eembe.png | ソフト&ハード設計実装セミナー | 8月5日(火) 申込締切日:7/25 10:00~17:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2068 | SoCとVitisツール | 2025年8月 | 202507251700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 8月5日(火)-6日(水) 申込締切日:7/25 10:00~17:30 | オンライン TC:8TC 現金:¥107,800 | 2069 | FPGAとVivadoツール | 2025年8月 | 202507251700 | 1 |

| embe.png | Zynq UltraScale+ MPSoCハードウェアデザイン | 8月5日(火)-6日(水) 申込締切日:7/25 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2070 | MPSoC/SoM | 2025年8月 | 202507251700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC VCU を使ったマルチメディアソリューション | 8月7日(木)-8日(金) 申込締切日:7/29 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2071 | MPSoC/SoM | 2025年8月 | 202507291700 | 1 |

| Vivado.png | Vivado Design Suite でのタイミング制約と解析 | 8月7日(木) 申込締切日:7/29 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2072 | FPGAとVivadoツール | 2025年8月 | 202507291700 | 1 |

| Vivado.png | Vivado Design Suite でのタイミング クロージャ | 8月8日(金) 申込締切日:7/30 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2073 | FPGAとVivadoツール | 2025年8月 | 202507301700 | 1 |

| Vivado.png | IP インテグレーターツールによる設計 | 8月19日(火) 申込締切日:8/7 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2074 | FPGAとVivadoツール | 2025年8月 | 202508071700 | 1 |

| lang.png | Designing with SystemVerilog | 8月21日(木)-22日(金) 申込締切日:8/12 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2075 | HDL言語と検証 | 2025年8月 | 202508121700 | 1 |

| Vivado.png | PCI Express デザイン | 8月21日(木)-22日(金) 申込締切日:8/12 10:00~17:30 | オンライン TC:12TC 現金:¥132,000 | 2076 | FPGAとVivadoツール | 2025年8月 | 202508121700 | 1 |

| eembe.png | Zynq SoC エンベデッドシステム開発 | 8月26日(火)-27日(水) 申込締切日:8/15 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2077 | SoCとVitisツール | 2025年8月 | 202508151700 | 1 |

| lang.png | [Verilog] Xilinx/Vivadoツールを使ったRTL設計初級 | 8月28日(木)-29日(金) 申込締切日:8/19 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2078 | HDL言語と検証 | 2025年8月 | 202508191700 | 1 |

| embe.png | Kria KV260 Vision AI | 8月28日(木)-29日(金) 申込締切日:8/19 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2079 | MPSoC/SoM | 2025年8月 | 202508191700 | 1 |

| AdovancedMin2.png | Embedded Heterogeneous Design | 9月2日(火)-3日(水) 申込締切日:8/22 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2081 | Versal Adaptive SoC | 2025年9月 | 202508221700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC: Quick Start | 9月4日(木) 申込締切日:8/26 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2083 | Versal Adaptive SoC | 2025年9月 | 202508261700 | 1 |

| AdovancedMin2.png | Versal AI Engine: Quick Start | 9月5日(金) 申込締切日:8/27 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2084 | Versal Adaptive SoC | 2025年9月 | 202508271700 | 1 |

| eembe.png | Migrating to the Vitis Unified IDE | 9月9日(火) 申込締切日:8/29 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2085 | SoCとVitisツール | 2025年9月 | 202508291700 | 1 |

| eembe.png | Embedded Systems Software Design Basic | 9月10日(水)-11日(木) 申込締切日:9/1 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 2086 | SoCとVitisツール | 2025年9月 | 202509011700 | 1 |

| eembe.png | Embedded Systems Software Design OS | 9月12日(金) 申込締切日:9/3 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2087 | SoCとVitisツール | 2025年9月 | 202509031700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC:アーキテクチャ | 9月9日(火)-10日(水) 申込締切日:8/29 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2088 | Versal Adaptive SoC | 2025年9月 | 202508291700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC:デザインメソドロジー | 9月11日(木)-12日(金) 申込締切日:9/2 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2089 | Versal Adaptive SoC | 2025年9月 | 202509021700 | 1 |

| AdovancedMin2.png | Versal Adaptive SoC:ネットワーク オン チップ | 9月17日(水) 申込締切日:9/5 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2090 | Versal Adaptive SoC | 2025年9月 | 202509051700 | 1 |

| Vivado.png | Vivado ロジック解析を使用したデバッグ 基礎編 | 9月17日(水) 申込締切日:9/5 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2091 | FPGAとVivadoツール | 2025年9月 | 202509051700 | 1 |

| lang.png | Verification with SystemVerilog | 9月18日(木)-19日(金) 申込締切日:9/8 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2092 | HDL言語と検証 | 2025年9月 | 202509081700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 9月18日(木)-19日(金) 申込締切日:9/8 10:00~17:30 | オンライン TC:8TC 現金:¥107,800 | 2093 | FPGAとVivadoツール | 2025年9月 | 202509081700 | 1 |

| lang.png | [VHDL] Xilinx/Vivadoツールを使ったRTL設計初級 | 9月18日(木)-19日(金) 申込締切日:9/8 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2094 | HDL言語と検証 | 2025年9月 | 202509081700 | 1 |

| eembe.png | VitisAIプラットフォーム | 9月24日(水)-25日(木) 申込締切日:9/10 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2095 | SoCとVitisツール | 2025年9月 | 202509101700 | 1 |

| Vivado.png | デザイン クロージャ テクニック デザイン&パワー | 9月24日(水) 申込締切日:9/10 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2096 | FPGAとVivadoツール | 2025年9月 | 202509101700 | 1 |

| Vivado.png | タイミングクロージャテクニックPart1 | 9月25日(木) 申込締切日:9/11 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2097 | FPGAとVivadoツール | 2025年9月 | 202509111700 | 1 |

| Vivado.png | タイミングクロージャテクニックPart2 | 9月26日(金) 申込締切日:9/12 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2098 | FPGAとVivadoツール | 2025年9月 | 202509121700 | 1 |

| AdovancedMin2.png | Versal Adaptive SoC Workshop【講義と演習】 | 9月30日(火) 申込締切日:9/17 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2099 | Versal Adaptive SoC | 2025年9月 | 202509171700 | 1 |

| AdovancedMin2.png | Versal Adaptive SoC Workshop【演習のみ】 | 9月30日(火) 申込締切日:9/17 13:30~18:00 | 新横浜(hdLab) TC:4TC 現金:¥44,000 | 2100 | Versal Adaptive SoC | 2025年9月 | 202509171700 | 1 |

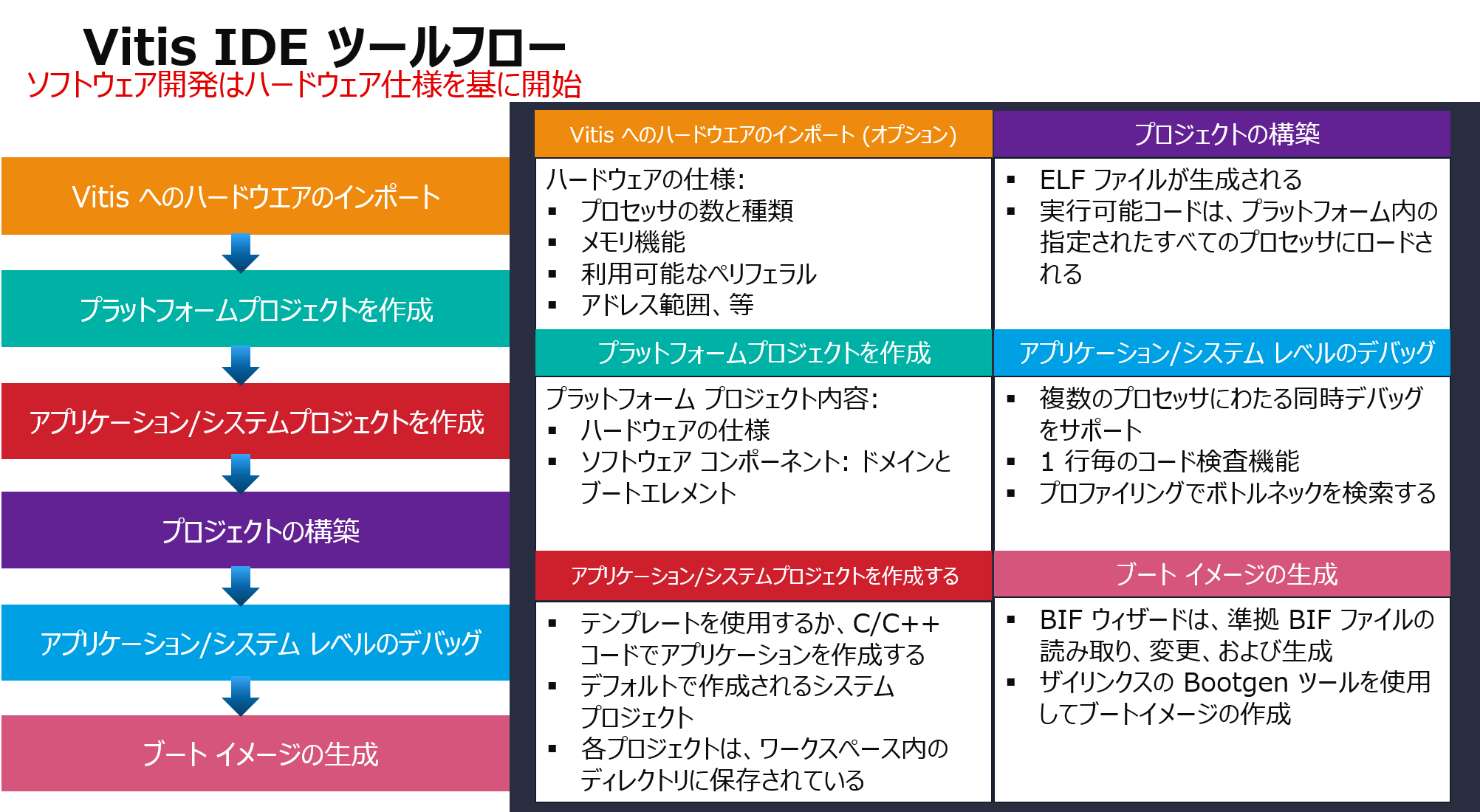

このコースでは、Vitis™統合ソフトウェアプラットフォームを使用したZynq®システムオンチップ(SoC)およびZynqUltraScale +™MPSoCのソフトウェア設計と開発に必要な概念、ツール、および手法を紹介します。

※「Zynq SoC エンベデッドシステムソフトウェア開発」のVitisSDK版です。

焦点は

▪Vitisツールの使用の基本を確認する

▪リソースアクセスのためのボードサポートパッケージ(BSP)のカスタマイズ

▪ザイリンクススタンドアロンライブラリの管理

▪デバイスドライバーを効果的に利用する

▪ARM®Cortex™-A9プロセッサ用のソフトウェアアプリケーションの開発

▪ユーザーアプリケーションのデバッグと統合

▪優れた設計を可能にするためのベストプラクティス

| コース名 | Vitisエンベデッドシステムソフトウエア開発 |

|---|---|

| ソフトウェアツール | Vitis 2020.1 |

| ハードウェア | ZCU104 |

| トレーニング期間 | 2日間 |

| 受講料 | 1名様 8TC or 107,800円(税込) |

| 受講対象者 | システムの設計と実装に関心のあるソフトウェア設計エンジニア ザイリンクス スタンドアロン ライブラリを使用したソフトウェア アプリケーションの開発とデバッグに関心のあるソフトウェア設計エンジニア |

| 受講要件 | ・一般的なデバッグ手法を含むCまたはC ++プログラミングの経験 ・デバイスドライバー、割り込みルーチン、スクリプトの作成と変更、ユーザーアプリケーション、ブートローダー操作などの組み込み処理システムの概念的な理解 |

| コース内容 | エンベデッドソフトウェア開発の概要 ユーザーアプリケーションを構築するプロセスの概要を説明します。 エンベデッド UltraFast 設計手法 組み込み設計手法を構成するさまざまな要素の概要を説明します。 Zynq-7000 SoC アーキテクチャの概要 Zynq-7000SoCアーキテクチャの概要を説明します。 Zynq UltraScale+ MPSoC アーキテクチャの概要 ZynqUltraScale+ MPSoCアーキテクチャの概要を説明します。 Vitis ソフトウェア開発ツールの推進 デバッグ可能なC / C ++アプリケーションを生成するために必要な基本的な動作を紹介します。 システム デバッガー デバッガー実行の基本を説明し、最も一般的に使用されるデバッグコマンドを示します。 スタンドアロン ソフトウェア プラットフォーム開発とコーディングのサポート ドライバ、ドメイン、オペレーティングシステム、ライブラリを含む、下層のソフトウェア作成を支援するためにザイリンクスが提供するさまざまなソフトウェアコンポーネントやレイヤについて説明します。また、スタンドアロン環境でコーディングするときに利用できる基本的なサービス(ライブラリ)についても説明します。 スタンドアロン用の FAT ファイル システム スタンドアロン/ベアメタルライブラリからFATファイルシステム(FFS)を導入します。 FFSは、メモリ領域をファイルシステムに効果的に変換するためのドライバとユーティリティを提供します。 リンカースクリプトの使用 リンカースクリプトの目的と一般的な使用方法を説明します。 SDK から Vitis プラットフォームへの移行 既存のザイリンクスSDKプロジェクトからVitisソフトウェア開発プロジェクトへの移行方法を説明します。 割り込みの概要 割り込みの概念、基本的な用語、および一般的な実装を紹介します。 ソフトウェア割り込み: 書き込み 割り込みをサポートするときにソフトウェアコーダーが考慮しなければならない考慮事項の多くについて説明します。 オペレーティング システム: 概要と概念 オペレーティングシステムの概念を紹介し、オペレーティングシステムを機能させる一般的な方法を提供します。 Linux: ハイレベルの概要 Linuxオペレーティングシステムの簡単な歴史、およびその使用方法を紹介します。 Linux ソフトウェア アプリケーション開発の概要 アプリケーションに関連する、基盤となるLinuxシステムの重要な部分に注目します。 PetaLinux ツールの駆動 (演習のみ) PetaLinuxツールを使用してアプリケーションを構築するために必要な基本概念を紹介します。 Vitis IDE で Linux アプリケーションの構築 Linuxソフトウェア開発にザイリンクスVitisIDEツールを使用する方法を紹介します。 ブートの概要 ZynqSoCデバイスおよびMicroBlazeプロセッサでプロセッサの起動がどのように処理されるかについて主なポイントを説明します。 ソフトウェアプロファイルの概要 ユーザーアプリケーションをプロファイリングする目的と手法を紹介します。 デバイスドライバーの理解 デバイスドライバーの概念と、組み込みシステムでの使用方法について説明します。 カスタムデバイスドライバー カスタムデバイスドライバーを正常に作成する方法について説明します。 |

| 関連する資料 | ※Xilinx社のサイトへ移動します。 デザインハブ Vitis エンベデッド ソフトウェア開発 |