Vivado ロジック解析を使用したデバッグ 基礎編

| カテゴリ | Courseへのリンク | 日程 | 会場、受講料 | 状況 | category | 開催月 | 締切時間 | Flag |

|---|---|---|---|---|---|---|---|---|

| embe.png | Zynq UltraScale+ MPSoC VCU を使ったマルチメディアソリューション | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 1 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC システムアーキテクチャ | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 2 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| Vivado.png | PCI Express デザイン | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 3 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC: Quick Start | 随時 | オンデマンド TC:6TC 現金:¥66,000 | 4 | Versal Adaptive SoC | オンデマンド | 203510311700 | 1 |

| lang.png | Verification with SystemVerilog | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 受付停止 | HDL言語と検証 | オンデマンド | 203510311700 | 1 |

| lang.png | Designing with SystemVerilog | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 受付停止 | HDL言語と検証 | オンデマンド | 203510311700 | 1 |

| eembe.png | Vitis HLSを使った高位合成 | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 7 | SoCとVitisツール | オンデマンド | 203510311700 | 1 |

| embe.png | Kria KV260 Vision AI | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 8 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 9 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| Vivado.png | Vivado Design Suite でのUltraFast設計手法 | 7月1日(火) 申込締切日:6/20 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2052 | FPGAとVivadoツール | 2025年7月 | 202506201700 | 1 |

| Vivado.png | Vivado Design Suite でのインプリメント手法 | 7月3日(木) 申込締切日:6/24 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2054 | FPGAとVivadoツール | 2025年7月 | 202506241700 | 1 |

| eembe.png | Vitis HLSを使った高位合成 | 7月8日(火)-9日(水) 申込締切日:6/27 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2056 | SoCとVitisツール | 2025年7月 | 202506271700 | 1 |

| eembe.png | Zynq SoC システムアーキテクチャ | 7月10日(木)-11日(金) 申込締切日:7/1 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2057 | SoCとVitisツール | 2025年7月 | 202507011700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC Boot and Platform Management | 7月15日(火)-16日(水) 申込締切日:7/4 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 開催中止 | MPSoC/SoM | 2025年7月 | 202507041700 | 0 |

| embe.png | OS and Hypervisors in Adaptive SoCs | 7月17日(木)-18日(金) 申込締切日:7/8 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 開催中止 | MPSoC/SoM | 2025年7月 | 202507081700 | 0 |

| lang.png | [Verilog] Xilinx/Vivadoツールを使ったRTL設計初級 | 7月17日(木)-18日(金) 申込締切日:7/8 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2060 | HDL言語と検証 | 2025年7月 | 202507081700 | 1 |

| lang.png | FPGA向けRTL設計スタイルガイドセミナー | 7月22日(火)-23日(水) 申込締切日:7/10 10:00~18:00 | 新横浜(hdLab) TC:8TC 現金:¥107,800 | 2061 | HDL言語と検証 | 2025年7月 | 202507101700 | 1 |

| eembe.png | Embedded Linux Development Using Yocto | 7月18日(金) 申込締切日:7/9 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 開催中止 | SoCとVitisツール | 2025年7月 | 202507091700 | 0 |

| embe.png | Zynq UltraScale+ MPSoC システムアーキテクチャ | 7月23日(水)-24日(木) 申込締切日:7/11 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2062 | MPSoC/SoM | 2025年7月 | 202507111700 | 1 |

| Vivado.png | Vivado Design Suite を使用したArtix-7 FPGA設計・開発入門 | 7月24日(木) 申込締切日:7/14 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2063 | FPGAとVivadoツール | 2025年7月 | 202507141700 | 1 |

| eembe.png | Migrating to the Vitis Unified IDE | 7月25日(金) 申込締切日:7/15 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2064 | SoCとVitisツール | 2025年7月 | 202507151700 | 1 |

| embe.png | Kria KV260 入門 | 8月1日(金) 申込締切日:7/23 13:00~18:00 | 新横浜(hdLab) TC:8TC 現金:TCのみ | 2067 | MPSoC/SoM | 2025年8月 | 202507231700 | 1 |

| eembe.png | ソフト&ハード設計実装セミナー | 8月5日(火) 申込締切日:7/25 10:00~17:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2068 | SoCとVitisツール | 2025年8月 | 202507251700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 8月5日(火)-6日(水) 申込締切日:7/25 10:00~17:30 | オンライン TC:8TC 現金:¥107,800 | 2069 | FPGAとVivadoツール | 2025年8月 | 202507251700 | 1 |

| embe.png | Zynq UltraScale+ MPSoCハードウェアデザイン | 8月5日(火)-6日(水) 申込締切日:7/25 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2070 | MPSoC/SoM | 2025年8月 | 202507251700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC VCU を使ったマルチメディアソリューション | 8月7日(木)-8日(金) 申込締切日:7/29 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2071 | MPSoC/SoM | 2025年8月 | 202507291700 | 1 |

| Vivado.png | Vivado Design Suite でのタイミング制約と解析 | 8月7日(木) 申込締切日:7/29 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2072 | FPGAとVivadoツール | 2025年8月 | 202507291700 | 1 |

| Vivado.png | Vivado Design Suite でのタイミング クロージャ | 8月8日(金) 申込締切日:7/30 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2073 | FPGAとVivadoツール | 2025年8月 | 202507301700 | 1 |

| Vivado.png | IP インテグレーターツールによる設計 | 8月19日(火) 申込締切日:8/7 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2074 | FPGAとVivadoツール | 2025年8月 | 202508071700 | 1 |

| lang.png | Designing with SystemVerilog | 8月21日(木)-22日(金) 申込締切日:8/12 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2075 | HDL言語と検証 | 2025年8月 | 202508121700 | 1 |

| Vivado.png | PCI Express デザイン | 8月21日(木)-22日(金) 申込締切日:8/12 10:00~17:30 | オンライン TC:12TC 現金:¥132,000 | 2076 | FPGAとVivadoツール | 2025年8月 | 202508121700 | 1 |

| eembe.png | Zynq SoC エンベデッドシステム開発 | 8月26日(火)-27日(水) 申込締切日:8/15 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2077 | SoCとVitisツール | 2025年8月 | 202508151700 | 1 |

| lang.png | [Verilog] Xilinx/Vivadoツールを使ったRTL設計初級 | 8月28日(木)-29日(金) 申込締切日:8/19 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2078 | HDL言語と検証 | 2025年8月 | 202508191700 | 1 |

| embe.png | Kria KV260 Vision AI | 8月28日(木)-29日(金) 申込締切日:8/19 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2079 | MPSoC/SoM | 2025年8月 | 202508191700 | 1 |

| AdovancedMin2.png | Embedded Heterogeneous Design | 9月2日(火)-3日(水) 申込締切日:8/22 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2081 | Versal Adaptive SoC | 2025年9月 | 202508221700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC: Quick Start | 9月4日(木) 申込締切日:8/26 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2083 | Versal Adaptive SoC | 2025年9月 | 202508261700 | 1 |

| AdovancedMin2.png | Versal AI Engine: Quick Start | 9月5日(金) 申込締切日:8/27 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2084 | Versal Adaptive SoC | 2025年9月 | 202508271700 | 1 |

| eembe.png | Migrating to the Vitis Unified IDE | 9月9日(火) 申込締切日:8/29 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2085 | SoCとVitisツール | 2025年9月 | 202508291700 | 1 |

| eembe.png | Embedded Systems Software Design Basic | 9月10日(水)-11日(木) 申込締切日:9/1 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 2086 | SoCとVitisツール | 2025年9月 | 202509011700 | 1 |

| eembe.png | Embedded Systems Software Design OS | 9月12日(金) 申込締切日:9/3 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2087 | SoCとVitisツール | 2025年9月 | 202509031700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC:アーキテクチャ | 9月9日(火)-10日(水) 申込締切日:8/29 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2088 | Versal Adaptive SoC | 2025年9月 | 202508291700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC:デザインメソドロジー | 9月11日(木)-12日(金) 申込締切日:9/2 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2089 | Versal Adaptive SoC | 2025年9月 | 202509021700 | 1 |

| AdovancedMin2.png | Versal Adaptive SoC:ネットワーク オン チップ | 9月17日(水) 申込締切日:9/5 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2090 | Versal Adaptive SoC | 2025年9月 | 202509051700 | 1 |

| Vivado.png | Vivado ロジック解析を使用したデバッグ 基礎編 | 9月17日(水) 申込締切日:9/5 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2091 | FPGAとVivadoツール | 2025年9月 | 202509051700 | 1 |

| lang.png | Verification with SystemVerilog | 9月18日(木)-19日(金) 申込締切日:9/8 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2092 | HDL言語と検証 | 2025年9月 | 202509081700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 9月18日(木)-19日(金) 申込締切日:9/8 10:00~17:30 | オンライン TC:8TC 現金:¥107,800 | 2093 | FPGAとVivadoツール | 2025年9月 | 202509081700 | 1 |

| lang.png | [VHDL] Xilinx/Vivadoツールを使ったRTL設計初級 | 9月18日(木)-19日(金) 申込締切日:9/8 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2094 | HDL言語と検証 | 2025年9月 | 202509081700 | 1 |

| eembe.png | VitisAIプラットフォーム | 9月24日(水)-25日(木) 申込締切日:9/10 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2095 | SoCとVitisツール | 2025年9月 | 202509101700 | 1 |

| Vivado.png | デザイン クロージャ テクニック デザイン&パワー | 9月24日(水) 申込締切日:9/10 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2096 | FPGAとVivadoツール | 2025年9月 | 202509101700 | 1 |

| Vivado.png | タイミングクロージャテクニックPart1 | 9月25日(木) 申込締切日:9/11 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2097 | FPGAとVivadoツール | 2025年9月 | 202509111700 | 1 |

| Vivado.png | タイミングクロージャテクニックPart2 | 9月26日(金) 申込締切日:9/12 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2098 | FPGAとVivadoツール | 2025年9月 | 202509121700 | 1 |

| AdovancedMin2.png | Versal Adaptive SoC Workshop【講義と演習】 | 9月30日(火) 申込締切日:9/17 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2099 | Versal Adaptive SoC | 2025年9月 | 202509171700 | 1 |

| AdovancedMin2.png | Versal Adaptive SoC Workshop【演習のみ】 | 9月30日(火) 申込締切日:9/17 13:30~18:00 | 新横浜(hdLab) TC:4TC 現金:¥44,000 | 2100 | Versal Adaptive SoC | 2025年9月 | 202509171700 | 1 |

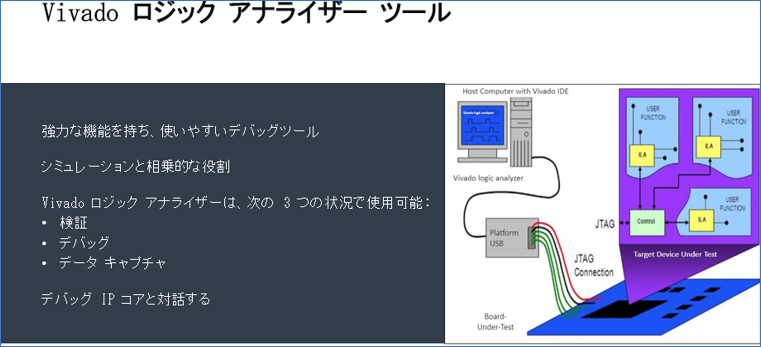

FPGA デザインがその複雑さを増しつつある中で、開発者は設計およびデバッグの時間を短縮する方法を常に

必要としています。

強力でありながら使いやすい VivadoR ロジック解析を使用するデバッグ ソリューションは、検証とデバッグに

かかる時間を最小限に抑えることができます。

このトレーニング コースでは、コアおよびツールについて紹介し、デザインを効率的にデバッグすることで

設計/開発の総時間の短縮を可能する方法を示します。

重点を置くのは次の点です。

・Vivado ロジック アナライザー (VLA) の概要

・Vivado のデバッグ機能を構成する基本的なコンポーネントの理解

・デザインをデバッグするための、基本的なプローブフローの理解

[このコースで学べること]

| コース名 | Vivado ロジック解析を使用したデバッグ 基礎編 |

|---|---|

| ソフトウェアツール | Vivado™ Design Suite 2019.1 |

| ハードウェア | ZCU104 または KCU105 または KC705 または NEXYS4 board |

| トレーニング期間 | 1日間 |

| 受講料 | 1名様 4TC or 53,900円(税込) |

| 受講対象者 | ・検証やデバッグに要する時間を短縮したいと考えるシステムおよびロジックの設計者 |

| 受講要件 | ・ハードウェア記述言語(VHDL/Verilog HDL)に関する基本的な知識を有する ・中級レベルの FPGA 設計スキル |

| コース内容 | ・Vivado Logic Analyzer入門 ・デバッグコア ・ネットリスト挿入フロー ・[演習] ネットリスト挿入フロー ・HDLインスタンシエーションフロー ・[演習] HDLインスタンシエーションフロー ・IPインテグレーターでのデバッグフロー ・[演習] IPインテグレーターでのデバッグフロー ・トリガー入門 |