Versal Adaptive SoC:ネットワーク オン チップ

| カテゴリ | Courseへのリンク | 日程 | 会場、受講料 | 状況 | category | 開催月 | 締切時間 | Flag |

|---|---|---|---|---|---|---|---|---|

| embe.png | Zynq UltraScale+ MPSoC VCU を使ったマルチメディアソリューション | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 1 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC システムアーキテクチャ | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 2 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| Vivado.png | PCI Express デザイン | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 3 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC: Quick Start | 随時 | オンデマンド TC:6TC 現金:¥66,000 | 4 | Versal Adaptive SoC | オンデマンド | 203510311700 | 1 |

| lang.png | Verification with SystemVerilog | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 受付停止 | HDL言語と検証 | オンデマンド | 203510311700 | 1 |

| lang.png | Designing with SystemVerilog | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 受付停止 | HDL言語と検証 | オンデマンド | 203510311700 | 1 |

| eembe.png | Vitis HLSを使った高位合成 | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 7 | SoCとVitisツール | オンデマンド | 203510311700 | 1 |

| embe.png | Kria KV260 Vision AI | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 8 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 9 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| eembe.png | Migrating to the Vitis Unified IDE | 6月3日(火) 申込締切日:5/23 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2035 | SoCとVitisツール | 2025年6月 | 202505231700 | 1 |

| eembe.png | Embedded Systems Software Design Basic | 6月4日(水)-5日(木) 申込締切日:5/26 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 2036 | SoCとVitisツール | 2025年6月 | 202505261700 | 1 |

| eembe.png | Embedded Systems Software Design OS | 6月6日(金) 申込締切日:5/28 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2037 | SoCとVitisツール | 2025年6月 | 202505281700 | 1 |

| Vivado.png | デザイン クロージャ テクニック デザイン&パワー | 6月5日(木) 申込締切日:5/27 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 開催中止 | FPGAとVivadoツール | 2025年6月 | 202505271700 | 0 |

| Vivado.png | タイミングクロージャテクニックPart1 | 6月9日(月) 申込締切日:5/29 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2039 | FPGAとVivadoツール | 2025年6月 | 202505291700 | 1 |

| Vivado.png | タイミングクロージャテクニックPart2 | 6月10日(火) 申込締切日:5/30 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2040 | FPGAとVivadoツール | 2025年6月 | 202505301700 | 1 |

| eembe.png | Vitis Model Composer | 6月10日(火)-11日(水) 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 開催中止 | SoCとVitisツール | 2025年6月 | 202505301700 | 0 |

| Vivado.png | IP インテグレーターツールによる設計 | 6月11日(水) 申込締切日:6/2 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 開催中止 | FPGAとVivadoツール | 2025年6月 | 202506021700 | 0 |

| eembe.png | PetaLinuxツールを使用したエンベデッドデザイン | 6月12日(木)-13日(金) 申込締切日:6/3 10:00~18:00 | 新横浜(hdLab) TC:8TC 現金:¥107,800 | 満席 | SoCとVitisツール | 2025年6月 | 202506031700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 6月19日(木)-20日(金) 申込締切日:6/10 10:00~17:30 | 新横浜(hdLab) TC:8TC 現金:¥107,800 | 2044 | FPGAとVivadoツール | 2025年6月 | 202506101700 | 1 |

| lang.png | Verification with SystemVerilog | 6月19日(木)-20日(金) 申込締切日:6/10 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2045 | HDL言語と検証 | 2025年6月 | 202506101700 | 1 |

| Vivado.png | Vivado Design Suite でのパーシャルリコンフィギュレーション | 6月23日(月) 申込締切日:6/12 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2050 | FPGAとVivadoツール | 2025年6月 | 202506121700 | 1 |

| Vivado.png | Vivado ロジック解析を使用したデバッグ 基礎編 | 6月24日(火) 申込締切日:6/13 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2046 | FPGAとVivadoツール | 2025年6月 | 202506131700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC: Quick Start | 6月25日(水) 申込締切日:6/16 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2047 | Versal Adaptive SoC | 2025年6月 | 202506161700 | 1 |

| lang.png | [VHDL] Xilinx/Vivadoツールを使ったRTL設計初級 | 6月26日(木)-27日(金) 申込締切日:6/17 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2048 | HDL言語と検証 | 2025年6月 | 202506171700 | 1 |

| eembe.png | VitisAIプラットフォーム | 6月26日(木)-27日(金) 申込締切日:6/17 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | SoCとVitisツール | 2025年6月 | 202506171700 | 0 |

| Vivado.png | Vivado Design Suite でのUltraFast設計手法 | 7月1日(火) 申込締切日:6/20 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2052 | FPGAとVivadoツール | 2025年7月 | 202506201700 | 1 |

| Vivado.png | Vivado Design Suite でのインプリメント手法 | 7月3日(木) 申込締切日:6/24 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2054 | FPGAとVivadoツール | 2025年7月 | 202506241700 | 1 |

| eembe.png | Vitis HLSを使った高位合成 | 7月8日(火)-9日(水) 申込締切日:6/27 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2056 | SoCとVitisツール | 2025年7月 | 202506271700 | 1 |

| eembe.png | Zynq SoC システムアーキテクチャ | 7月10日(木)-11日(金) 申込締切日:7/1 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2057 | SoCとVitisツール | 2025年7月 | 202507011700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC Boot and Platform Management | 7月15日(火)-16日(水) 申込締切日:7/4 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 2058 | MPSoC/SoM | 2025年7月 | 202507041700 | 1 |

| embe.png | OS and Hypervisors in Adaptive SoCs | 7月17日(木)-18日(金) 申込締切日:7/8 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 2059 | MPSoC/SoM | 2025年7月 | 202507081700 | 1 |

| lang.png | [Verilog] Xilinx/Vivadoツールを使ったRTL設計初級 | 7月17日(木)-18日(金) 申込締切日:7/8 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2060 | HDL言語と検証 | 2025年7月 | 202507081700 | 1 |

| lang.png | FPGA向けRTL設計スタイルガイドセミナー | 7月22日(火)-23日(水) 申込締切日:7/10 10:00~18:00 | 新横浜(hdLab) TC:8TC 現金:¥107,800 | 2061 | HDL言語と検証 | 2025年7月 | 202507101700 | 1 |

| eembe.png | Embedded Linux Development Using Yocto | 7月18日(金) 申込締切日:7/9 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2055 | SoCとVitisツール | 2025年7月 | 202507091700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC システムアーキテクチャ | 7月23日(水)-24日(木) 申込締切日:7/11 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2062 | MPSoC/SoM | 2025年7月 | 202507111700 | 1 |

| Vivado.png | Vivado Design Suite を使用したArtix-7 FPGA設計・開発入門 | 7月24日(木) 申込締切日:7/14 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2063 | FPGAとVivadoツール | 2025年7月 | 202507141700 | 1 |

| eembe.png | Migrating to the Vitis Unified IDE | 7月25日(金) 申込締切日:7/15 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2064 | SoCとVitisツール | 2025年7月 | 202507151700 | 1 |

| embe.png | Kria KV260 入門 | 8月1日(金) 申込締切日:7/23 13:00~18:00 | 新横浜(hdLab) TC:8TC 現金:TCのみ | 2067 | MPSoC/SoM | 2025年8月 | 202507231700 | 1 |

| eembe.png | ソフト&ハード設計実装セミナー | 8月5日(火) 申込締切日:7/25 10:00~17:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2068 | SoCとVitisツール | 2025年8月 | 202507251700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 8月5日(火)-6日(水) 申込締切日:7/25 10:00~17:30 | オンライン TC:8TC 現金:¥107,800 | 2069 | FPGAとVivadoツール | 2025年8月 | 202507251700 | 1 |

| embe.png | Zynq UltraScale+ MPSoCハードウェアデザイン | 8月5日(火)-6日(水) 申込締切日:7/25 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2070 | MPSoC/SoM | 2025年8月 | 202507251700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC VCU を使ったマルチメディアソリューション | 8月7日(木)-8日(金) 申込締切日:7/29 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2071 | MPSoC/SoM | 2025年8月 | 202507291700 | 1 |

| Vivado.png | Vivado Design Suite でのタイミング制約と解析 | 8月7日(木) 申込締切日:7/29 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2072 | FPGAとVivadoツール | 2025年8月 | 202507291700 | 1 |

| Vivado.png | Vivado Design Suite でのタイミング クロージャ | 8月8日(金) 申込締切日:7/30 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2073 | FPGAとVivadoツール | 2025年8月 | 202507301700 | 1 |

| Vivado.png | IP インテグレーターツールによる設計 | 8月19日(火) 申込締切日:8/7 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2074 | FPGAとVivadoツール | 2025年8月 | 202508071700 | 1 |

| lang.png | Designing with SystemVerilog | 8月21日(木)-22日(金) 申込締切日:8/12 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2075 | HDL言語と検証 | 2025年8月 | 202508121700 | 1 |

| Vivado.png | PCI Express デザイン | 8月21日(木)-22日(金) 申込締切日:8/12 10:00~17:30 | オンライン TC:12TC 現金:¥132,000 | 2076 | FPGAとVivadoツール | 2025年8月 | 202508121700 | 1 |

| eembe.png | Zynq SoC エンベデッドシステム開発 | 8月26日(火)-27日(水) 申込締切日:8/15 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2077 | SoCとVitisツール | 2025年8月 | 202508151700 | 1 |

| lang.png | [Verilog] Xilinx/Vivadoツールを使ったRTL設計初級 | 8月28日(木)-29日(金) 申込締切日:8/19 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2078 | HDL言語と検証 | 2025年8月 | 202508191700 | 1 |

| embe.png | Kria KV260 Vision AI | 8月28日(木)-29日(金) 申込締切日:8/19 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2079 | MPSoC/SoM | 2025年8月 | 202508191700 | 1 |

| AdovancedMin2.png | Embedded Heterogeneous Design | 9月2日(火)-3日(水) 申込締切日:8/22 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2081 | Versal Adaptive SoC | 2025年9月 | 202508221700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC: Quick Start | 9月4日(木) 申込締切日:8/26 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2083 | Versal Adaptive SoC | 2025年9月 | 202508261700 | 1 |

| AdovancedMin2.png | Versal AI Engine: Quick Start | 9月5日(金) 申込締切日:8/27 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2084 | Versal Adaptive SoC | 2025年9月 | 202508271700 | 1 |

| eembe.png | Migrating to the Vitis Unified IDE | 9月9日(火) 申込締切日:8/29 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2085 | SoCとVitisツール | 2025年9月 | 202508291700 | 1 |

| eembe.png | Embedded Systems Software Design Basic | 9月10日(水)-11日(木) 申込締切日:9/1 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 2086 | SoCとVitisツール | 2025年9月 | 202509011700 | 1 |

| eembe.png | Embedded Systems Software Design OS | 9月12日(金) 申込締切日:9/3 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2087 | SoCとVitisツール | 2025年9月 | 202509031700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC:アーキテクチャ | 9月9日(火)-10日(水) 申込締切日:8/29 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2088 | Versal Adaptive SoC | 2025年9月 | 202508291700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC:デザインメソドロジー | 9月11日(木)-12日(金) 申込締切日:9/2 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2089 | Versal Adaptive SoC | 2025年9月 | 202509021700 | 1 |

| AdovancedMin2.png | Versal Adaptive SoC:ネットワーク オン チップ | 9月17日(水) 申込締切日:9/5 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2090 | Versal Adaptive SoC | 2025年9月 | 202509051700 | 1 |

| Vivado.png | Vivado ロジック解析を使用したデバッグ 基礎編 | 9月17日(水) 申込締切日:9/5 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2091 | FPGAとVivadoツール | 2025年9月 | 202509051700 | 1 |

| lang.png | Verification with SystemVerilog | 9月18日(木)-19日(金) 申込締切日:9/8 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2092 | HDL言語と検証 | 2025年9月 | 202509081700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 9月18日(木)-19日(金) 申込締切日:9/8 10:00~17:30 | オンライン TC:8TC 現金:¥107,800 | 2093 | FPGAとVivadoツール | 2025年9月 | 202509081700 | 1 |

| lang.png | [VHDL] Xilinx/Vivadoツールを使ったRTL設計初級 | 9月18日(木)-19日(金) 申込締切日:9/8 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2094 | HDL言語と検証 | 2025年9月 | 202509081700 | 1 |

| eembe.png | VitisAIプラットフォーム | 9月24日(水)-25日(木) 申込締切日:9/10 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2095 | SoCとVitisツール | 2025年9月 | 202509101700 | 1 |

| Vivado.png | デザイン クロージャ テクニック デザイン&パワー | 9月24日(水) 申込締切日:9/10 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2096 | FPGAとVivadoツール | 2025年9月 | 202509101700 | 1 |

| Vivado.png | タイミングクロージャテクニックPart1 | 9月25日(木) 申込締切日:9/11 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2097 | FPGAとVivadoツール | 2025年9月 | 202509111700 | 1 |

| Vivado.png | タイミングクロージャテクニックPart2 | 9月26日(金) 申込締切日:9/12 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2098 | FPGAとVivadoツール | 2025年9月 | 202509121700 | 1 |

| AdovancedMin2.png | Versal Adaptive SoC Workshop【講義と演習】 | 9月30日(火) 申込締切日:9/17 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2099 | Versal Adaptive SoC | 2025年9月 | 202509171700 | 1 |

| AdovancedMin2.png | Versal Adaptive SoC Workshop【演習のみ】 | 9月30日(火) 申込締切日:9/17 13:30~18:00 | 新横浜(hdLab) TC:4TC 現金:¥44,000 | 2100 | Versal Adaptive SoC | 2025年9月 | 202509171700 | 1 |

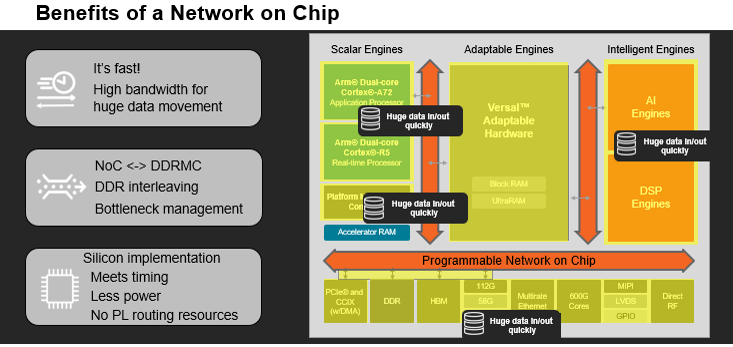

このコースでは、ザイリンクスデバイスに精通しているユーザーにVersal™ACAPネットワークオンチップ(NoC)を紹介します。 このコースでは、Versalデバイスの主要コンポーネントの概要を説明するだけでなく、NoCを使用してデバイス内でデータを効率的に移動する方法についても説明します。

このコースの重点は次のとおりです。

▪VersalACAPでNoCアーキテクチャを構成する主要コンポーネント

▪NoCを使用した基本設計の実装

▪効率的なデータ移動のためのNoCの構成

2023.1のアップデート:「 Versal NoC and DDR Memory Controllers」のLabが追加になりました。

【ご注意下さい】

このコースの説明は日本語で行いますが、テキストは英語となります。

| コース名 | Versal ACAP: ネットワーク オン チップ |

|---|---|

| ソフトウェアツール | Vivado ML Edition 2023.1 |

| トレーニング期間 | 1日間 |

| 受講料 | 1名様 6TC or 66,000円(税込) |

| 受講対象者 | 既存デバイスから移行するハードウエアエンジニア、システムアーキテクト Versal ACAPで始めるハードウエアエンジニア、システムアーキテクト |

| 受講要件 | ・ザイリンクスデバイスのアーキテクチャクラスを受講済みまたは相当の知識を有する ・Vivado Design Suiteに精通 |

| コース内容 | ▪ Architecture Overview for Existing Xilinx Users Introduces to students that already have familiarity with Xilinx architectures to the new and updated features found in the Versal ACAP devices. {Lecture} ▪ Versal ACAPs Compared to Zynq UltraScale+ Devices The Versal ACAP has a number of similarities to the Zynq® UltraScale+™ MPSoC devices. Understanding what is the same, what is different, and what is brand new helps put this powerful new part into context. {Lecture} ▪ NoC Introduction and Concepts Reviews the basic vocabulary and high-level operations of the NoC. {Lecture, Lab} ▪ NoC Architecture Provides the first deep dive into the sub-blocks of the NoC and how they are used. Describes how the NoC is accessed from the programmable logic. {Lecture ▪Design Tool Flow Overview Designers come to the Versal ACAP devices with different goals. This module explores how traditional FPGA designers, embedded developers, and accelerated system designers would use the various tools available in the Xilinx toolbox. {Lecture} ▪ NoC DDR Memory Controller The integration between the NoC pathways and the DDR memory controllers must be understood to have efficient data movement on and off chip. This discussion of the NoC's DDR memory controller blocks provides the background for properly selecting and configuring DDR memory and the memory controller for effective use. {Lecture,Lab} ▪ NoC Performance Tuning Synthesizes everything about the NoC and its DDRMCs, illustrating how to fine tune the NoC for the best performance. {Lecture, Lab} ▪ System Design Migration Describes how different users will leverage tools and processes to migrate their designs to the Versal ACAP devices. {Lecture} |

| 関連する資料 |