Zynq UltraScale+ MPSoC ハードウェアデザイン

| カテゴリ | Courseへのリンク | 日程 | 会場、受講料 | 状況 | category | 開催月 | 締切時間 | Flag |

|---|---|---|---|---|---|---|---|---|

| embe.png | Zynq UltraScale+ MPSoC VCU を使ったマルチメディアソリューション | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 1 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC システムアーキテクチャ | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 2 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| Vivado.png | PCI Express デザイン | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 3 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC: Quick Start | 随時 | オンデマンド TC:6TC 現金:¥66,000 | 4 | Versal Adaptive SoC | オンデマンド | 203510311700 | 1 |

| lang.png | Verification with SystemVerilog | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 受付停止 | HDL言語と検証 | オンデマンド | 203510311700 | 1 |

| lang.png | Designing with SystemVerilog | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 受付停止 | HDL言語と検証 | オンデマンド | 203510311700 | 1 |

| eembe.png | Vitis HLSを使った高位合成 | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 7 | SoCとVitisツール | オンデマンド | 203510311700 | 1 |

| embe.png | Kria KV260 Vision AI | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 8 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 9 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC Boot and Platform Management | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 10 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| AdovancedMin2.png | Embedded Heterogeneous Design | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 11 | Versal Adaptive SoC | オンデマンド | 203510311700 | 1 |

| eembe.png | Vitis Model Composer | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 12 | SoCとVitisツール | オンデマンド | 203510311700 | 1 |

| Vivado.png | IP インテグレーターツールによる設計 | 随時 | オンデマンド TC:6TC 現金:¥66,000 | 13 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC ハードウェアデザイン | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 14 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| eembe.png | PetaLinuxツールを使用したエンベデッドデザイン | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 15 | SoCとVitisツール | オンデマンド | 203510311700 | 1 |

| Vivado.png | Vivado Design Suite でのUltraFast設計手法 | 随時 | オンデマンド TC:4TC 現金:¥53,900 | 16 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| Vivado.png | Spartan UltraScale+ FPGA: Architecture | 2月3日(火)-4日(水) 申込締切日:1/23 10:00~17:30 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | FPGAとVivadoツール | 2026年2月 | 202601231700 | 0 |

| embe.png | Zynq UltraScale+ MPSoC ハードウェアデザイン | 2月3日(火)-4日(水) 申込締切日:1/23 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | MPSoC/SoM | 2026年2月 | 202601231700 | 0 |

| Vivado.png | Vivado Design Suite でのタイミング制約と解析 | 2月5日(木) 申込締切日:1/27 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2176 | FPGAとVivadoツール | 2026年2月 | 202601271700 | 1 |

| Vivado.png | Vivado Design Suite でのタイミング クロージャ | 2月6日(金) 申込締切日:1/28 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2177 | FPGAとVivadoツール | 2026年2月 | 202601281700 | 1 |

| lang.png | Designing with SystemVerilog | 2月9日(月)-10日(火) 申込締切日:1/29 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 開催中止 | HDL言語と検証 | 2026年2月 | 202601291700 | 0 |

| eembe.png | ソフト&ハード システム設計セミナー | 2月9日(月)-10日(火) 申込締切日:1/29 10:00~17:00 | オンライン TC:16TC 現金:¥176,000 | 2179 | SoCとVitisツール | 2026年2月 | 202601291700 | 1 |

| eembe.png | ZYBOを使ったカラーバー発生回路作成 | 2月10日(火) 申込締切日:1/30 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 開催中止 | SoCとVitisツール | 2026年2月 | 202601301700 | 0 |

| lang.png | [Verilog] Xilinx/Vivadoツールを使ったRTL設計初級 | 2月12日(木)-13日(金) 申込締切日:2/2 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2181 | HDL言語と検証 | 2026年2月 | 202602021700 | 1 |

| eembe.png | Vitis Model Composer | 2月12日(木)-13日(金) 申込締切日:2/2 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | SoCとVitisツール | 2026年2月 | 202602021700 | 0 |

| eembe.png | Zynq SoC システムアーキテクチャ | 2月17日(火)-18日(水) 申込締切日:2/5 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2184 | SoCとVitisツール | 2026年2月 | 202602051700 | 1 |

| Vivado.png | PCI Express デザイン | 2月19日(木)-20日(金) 申込締切日:2/9 10:00~17:30 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | FPGAとVivadoツール | 2026年2月 | 202602091700 | 0 |

| Vivado.png | Vivado Design Suite ツールフロー | 2月19日(木) 申込締切日:2/9 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 開催中止 | FPGAとVivadoツール | 2026年2月 | 202602091700 | 0 |

| AdovancedMin2.png | Versal adaptive SoC: Quick Start | 2月25日(水) 申込締切日:2/13 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 開催中止 | Versal Adaptive SoC | 2026年2月 | 202602131700 | 0 |

| AdovancedMin2.png | Embedded Heterogeneous Design | 2月26日(木)-27日(金) 申込締切日:2/16 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | Versal Adaptive SoC | 2026年2月 | 202602161700 | 0 |

| Vivado.png | デザイン クロージャ テクニック デザイン&パワー | 3月3日(火) 申込締切日:2/19 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 開催中止 | FPGAとVivadoツール | 2026年3月 | 202602191700 | 0 |

| AdovancedMin2.png | Versal AI Engine 1: アーキテクチャとデザインフロー | 3月3日(火)-4日(水) 申込締切日:2/19 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | Versal Adaptive SoC | 2026年3月 | 202602191700 | 0 |

| eembe.png | Embedded Systems Software Design Basic | 3月3日(火)-4日(水) 申込締切日:2/19 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 開催中止 | SoCとVitisツール | 2026年3月 | 202602191700 | 0 |

| eembe.png | Embedded Systems Software Design OS | 3月5日(木) 申込締切日:2/24 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2193 | SoCとVitisツール | 2026年3月 | 202602241700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC:アーキテクチャ | 3月5日(木)-6日(金) 申込締切日:2/24 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | Versal Adaptive SoC | 2026年3月 | 202602241700 | 0 |

| Vivado.png | Vivado Design Suite を使用したArtix-7 FPGA設計・開発入門 | 3月6日(金) 申込締切日:2/25 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2195 | FPGAとVivadoツール | 2026年3月 | 202602251700 | 1 |

| Vivado.png | Vivado ロジック解析を使用したデバッグ 基礎編 | 3月10日(火) 申込締切日:2/27 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2196 | FPGAとVivadoツール | 2026年3月 | 202602271700 | 1 |

| eembe.png | Migrating to the Vitis Unified IDE | 3月11日(水) 申込締切日:3/2 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 開催中止 | SoCとVitisツール | 2026年3月 | 202603021700 | 0 |

| embe.png | OS and Hypervisors in Adaptive SoCs | 3月12日(木)-13日(金) 申込締切日:3/3 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 開催中止 | MPSoC/SoM | 2026年3月 | 202603031700 | 0 |

| Vivado.png | タイミングクロージャテクニックPart1 | 3月12日(木) 申込締切日:3/3 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2199 | FPGAとVivadoツール | 2026年3月 | 202603031700 | 1 |

| Vivado.png | タイミングクロージャテクニックPart2 | 3月13日(金) 申込締切日:3/4 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2200 | FPGAとVivadoツール | 2026年3月 | 202603041700 | 1 |

| lang.png | Verification with SystemVerilog | 3月16日(月)-17日(火) 申込締切日:3/5 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2201 | HDL言語と検証 | 2026年3月 | 202603051700 | 1 |

| eembe.png | Zynq SoC エンベデッドシステム開発 | 3月16日(月)-17日(火) 申込締切日:3/5 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2202 | SoCとVitisツール | 2026年3月 | 202603051700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 3月18日(水)-19日(木) 申込締切日:3/9 10:00~17:30 | 新横浜(hdLab) TC:8TC 現金:¥107,800 | 2203 | FPGAとVivadoツール | 2026年3月 | 202603091700 | 1 |

| lang.png | [VHDL] Xilinx/Vivadoツールを使ったRTL設計初級 | 3月18日(水)-19日(木) 申込締切日:3/9 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2204 | HDL言語と検証 | 2026年3月 | 202603091700 | 1 |

| eembe.png | ソフト&ハード設計実装セミナー | 3月23日(月) 申込締切日:3/11 10:00~17:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2205 | SoCとVitisツール | 2026年3月 | 202603111700 | 1 |

| embe.png | Kria KV260 入門 | 3月24日(火) 申込締切日:3/12 13:00~18:00 | 新横浜(hdLab) TC:8TC 現金:TCのみ | 2206 | MPSoC/SoM | 2026年3月 | 202603121700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC:デザインメソドロジーPart1 | 3月24日(火)-25日(水) 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | Versal Adaptive SoC | 2026年3月 | 202603121700 | 0 |

| AdovancedMin2.png | Versal adaptive SoC:デザインメソドロジーPart2 | 3月26日(木) 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 開催中止 | Versal Adaptive SoC | 2026年3月 | 202603161700 | 0 |

| AdovancedMin2.png | Versal Adaptive SoC:ネットワーク オン チップ | 3月27日(金) 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 開催中止 | Versal Adaptive SoC | 2026年3月 | 202603171700 | 0 |

| embe.png | Zynq UltraScale+ MPSoC Boot and Platform Management | 3月30日(月)-31日(火) 申込締切日:3/18 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 2210 | MPSoC/SoM | 2026年3月 | 202603181700 | 1 |

| Vivado.png | Vivado Design Suite を使用したArtix-7 FPGA設計・開発入門 | 4月7日(火) 申込締切日:3/27 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2212 | FPGAとVivadoツール | 2026年4月 | 202603271700 | 1 |

| lang.png | [Verilog] Xilinx/Vivadoツールを使ったRTL設計初級 | 4月7日(火)-8日(水) 申込締切日:3/27 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2213 | HDL言語と検証 | 2026年4月 | 202603271700 | 1 |

| Vivado.png | Vivado Design Suite でのUltraFast設計手法 | 4月9日(木) 申込締切日:3/31 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2214 | FPGAとVivadoツール | 2026年4月 | 202603311700 | 1 |

| eembe.png | Vitis HLSを使った高位合成 | 4月9日(木)-10日(金) 申込締切日:3/31 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2215 | SoCとVitisツール | 2026年4月 | 202603311700 | 1 |

| eembe.png | Zynq SoC システムアーキテクチャ | 4月14日(火)-15日(水) 申込締切日:4/3 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2216 | SoCとVitisツール | 2026年4月 | 202604031700 | 1 |

| eembe.png | ARTYを使用したMicroBlaze-v開発入門 | 4月15日(水) 申込締切日:4/6 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2217 | SoCとVitisツール | 2026年4月 | 202604061700 | 1 |

| Vivado.png | Vivado Design Suite でのインプリメント手法 | 4月16日(木) 申込締切日:4/7 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2218 | FPGAとVivadoツール | 2026年4月 | 202604071700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 4月20日(月)-21日(火) 申込締切日:4/9 10:00~17:30 | オンライン TC:8TC 現金:¥107,800 | 2219 | FPGAとVivadoツール | 2026年4月 | 202604091700 | 1 |

| eembe.png | Yoctoを使用した組み込みLinux開発 | 4月22日(水) 申込締切日:4/13 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2220 | SoCとVitisツール | 2026年4月 | 202604131700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC システムアーキテクチャ | 4月23日(木)-24日(金) 申込締切日:4/14 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2221 | MPSoC/SoM | 2026年4月 | 202604141700 | 1 |

| lang.png | FPGA向けRTL設計スタイルガイドセミナー | 4月23日(木)-24日(金) 申込締切日:4/14 10:00~18:00 | 新横浜(hdLab) TC:8TC 現金:¥107,800 | 2222 | HDL言語と検証 | 2026年4月 | 202604141700 | 1 |

※2024年8月開催分より、講座内容を刷新し、開催日数は2日間となります。

あわせて、受講料も改定しておりますのでご注意下さい。

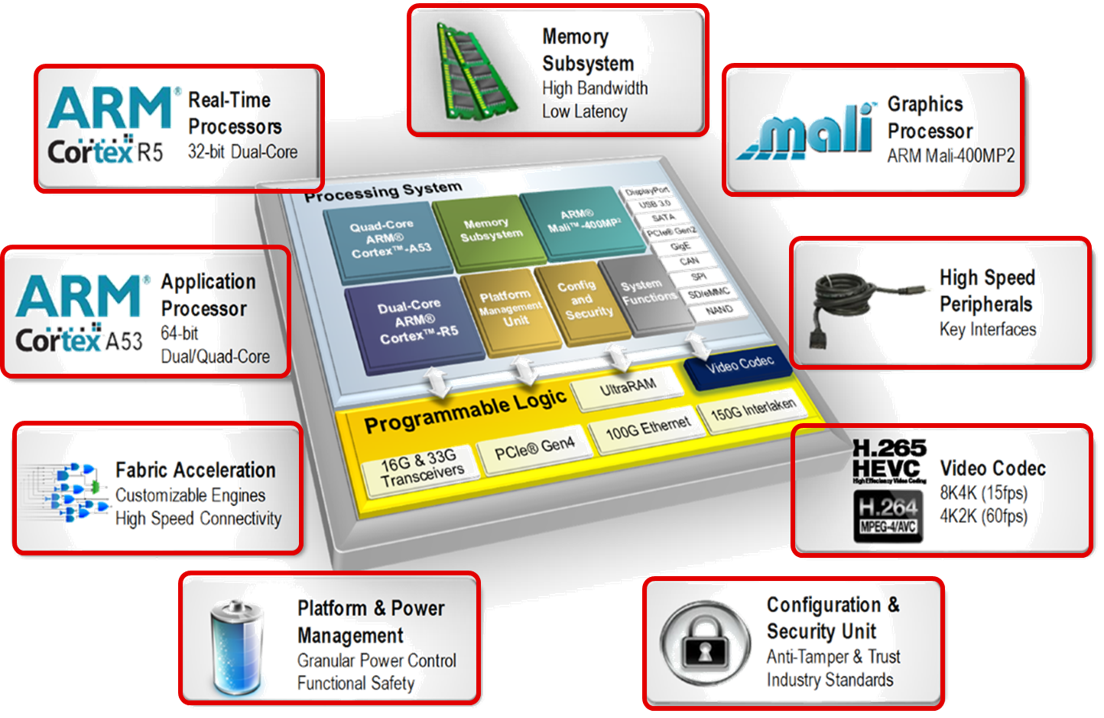

このコースでは、ハードウェア設計者向けにZynq® UltraScale+™ MPSoC デバイスのアーキテクチャと機能を説明します。

[このコースで学べること]

Zynq UltraScale+ MPSoC の概要

| コース名 | Zynq UltraScale+ MPSoC ハードウェアデザイン |

|---|---|

| ソフトウェアツール | ・Vivado Design Suite 2023.1 ・Vitis unified software platform 2023.1 |

| ハードウェア | ・Architecture: Zynq UltraScale+ MPSoC ・Demo board: ZCU104 |

| トレーニング期間 | 2日間 |

| 受講料 | 1名様 12TC or 132,000円(税込) |

| 受講対象者 | Zynq UltraScale+ MPSoC デバイスの主要ハードウェアの構造を理解したい方 Zynq UltraScale+ MPSoC デバイスの設計をするハードウエアエンジニア |

| 受講要件 | Zynq UltraScale+ MPSoC に関する基礎知識 Vivado および Vitisツールの基本的な知識 |

| コース内容 | Day 1 アプリケーション プロセッシング ユニット ・ArmR Cortex・-A53 プロセッサ ・アーキテクチャ拡張 ・64-ビット アーキテクチャの機能 ・例外処理 ・キャッシュコヒーレンシ ・HW-SW の仮想化 ・ハイパーバイザー: 概要 ・仮想化ハードウェアのサポート リアルタイム プロセッシング ユニット ・L1 および L2 キャッシュ ・クロッキング、パワー、リセット TCM アーキテクチャ QEMU ・アプリケーション開発とデバッグ ブート ・ブートとコンフィグレーション ・ブート イメージ FSBL (第 1 段階ブートローダー) Day 2 ビデオ ・ビデオ コーデック ユニットの概要 ・VCU アーキテクチャ システム保護 ・システム メモリ管理ユニット ・ペリフェラル保護ユニット ・メモリ保護ユニット クロックおよびリセット ・クロック ・PS リセット AXI ・バリエーション ・トランザクション 消費電力管理と PMU ・電源ドメイン ・PMU の概要 ・PMU システムアーキテクチャ ・PMUと IPI クロストリガを使ったデバッグ ・クロストリガを使ったデバッグ ※予告なくコース内容に若干の変更がはいる場合があります。 ※進行状況により内容が変わる場合があります。 ※オンライン開催場合、演習は講師のデモとなります。 |