Versal Adaptive SoC:アーキテクチャ

| カテゴリ | Courseへのリンク | 日程 | 会場、受講料 | 状況 | category | 開催月 | 締切時間 | Flag |

|---|---|---|---|---|---|---|---|---|

| embe.png | Zynq UltraScale+ MPSoC VCU を使ったマルチメディアソリューション | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 1 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC システムアーキテクチャ | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 2 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| Vivado.png | PCI Express デザイン | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 3 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC: Quick Start | 随時 | オンデマンド TC:6TC 現金:¥66,000 | 4 | Versal Adaptive SoC | オンデマンド | 203510311700 | 1 |

| lang.png | Verification with SystemVerilog | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 受付停止 | HDL言語と検証 | オンデマンド | 203510311700 | 1 |

| lang.png | Designing with SystemVerilog | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 受付停止 | HDL言語と検証 | オンデマンド | 203510311700 | 1 |

| eembe.png | Vitis HLSを使った高位合成 | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 7 | SoCとVitisツール | オンデマンド | 203510311700 | 1 |

| embe.png | Kria KV260 Vision AI | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 8 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 9 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC Boot and Platform Management | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 10 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| AdovancedMin2.png | Embedded Heterogeneous Design | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 11 | Versal Adaptive SoC | オンデマンド | 203510311700 | 1 |

| eembe.png | Vitis Model Composer | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 12 | SoCとVitisツール | オンデマンド | 203510311700 | 1 |

| Vivado.png | IP インテグレーターツールによる設計 | 随時 | オンデマンド TC:6TC 現金:¥66,000 | 13 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC ハードウェアデザイン | 随時 | オンデマンド TC:12TC 現金:¥132,000 | 14 | MPSoC/SoM | オンデマンド | 203510311700 | 1 |

| eembe.png | PetaLinuxツールを使用したエンベデッドデザイン | 随時 | オンデマンド TC:8TC 現金:¥107,800 | 15 | SoCとVitisツール | オンデマンド | 203510311700 | 1 |

| Vivado.png | Vivado Design Suite でのUltraFast設計手法 | 随時 | オンデマンド TC:4TC 現金:¥53,900 | 16 | FPGAとVivadoツール | オンデマンド | 203510311700 | 1 |

| Vivado.png | Spartan UltraScale+ FPGA: Architecture | 2月3日(火)-4日(水) 申込締切日:1/23 10:00~17:30 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | FPGAとVivadoツール | 2026年2月 | 202601231700 | 0 |

| embe.png | Zynq UltraScale+ MPSoC ハードウェアデザイン | 2月3日(火)-4日(水) 申込締切日:1/23 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | MPSoC/SoM | 2026年2月 | 202601231700 | 0 |

| Vivado.png | Vivado Design Suite でのタイミング制約と解析 | 2月5日(木) 申込締切日:1/27 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2176 | FPGAとVivadoツール | 2026年2月 | 202601271700 | 1 |

| Vivado.png | Vivado Design Suite でのタイミング クロージャ | 2月6日(金) 申込締切日:1/28 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2177 | FPGAとVivadoツール | 2026年2月 | 202601281700 | 1 |

| lang.png | Designing with SystemVerilog | 2月9日(月)-10日(火) 申込締切日:1/29 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 開催中止 | HDL言語と検証 | 2026年2月 | 202601291700 | 0 |

| eembe.png | ソフト&ハード システム設計セミナー | 2月9日(月)-10日(火) 申込締切日:1/29 10:00~17:00 | オンライン TC:16TC 現金:¥176,000 | 2179 | SoCとVitisツール | 2026年2月 | 202601291700 | 1 |

| eembe.png | ZYBOを使ったカラーバー発生回路作成 | 2月10日(火) 申込締切日:1/30 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 開催中止 | SoCとVitisツール | 2026年2月 | 202601301700 | 0 |

| lang.png | [Verilog] Xilinx/Vivadoツールを使ったRTL設計初級 | 2月12日(木)-13日(金) 申込締切日:2/2 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2181 | HDL言語と検証 | 2026年2月 | 202602021700 | 1 |

| eembe.png | Vitis Model Composer | 2月12日(木)-13日(金) 申込締切日:2/2 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | SoCとVitisツール | 2026年2月 | 202602021700 | 0 |

| eembe.png | Zynq SoC システムアーキテクチャ | 2月17日(火)-18日(水) 申込締切日:2/5 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2184 | SoCとVitisツール | 2026年2月 | 202602051700 | 1 |

| Vivado.png | PCI Express デザイン | 2月19日(木)-20日(金) 申込締切日:2/9 10:00~17:30 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | FPGAとVivadoツール | 2026年2月 | 202602091700 | 0 |

| Vivado.png | Vivado Design Suite ツールフロー | 2月19日(木) 申込締切日:2/9 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 開催中止 | FPGAとVivadoツール | 2026年2月 | 202602091700 | 0 |

| AdovancedMin2.png | Versal adaptive SoC: Quick Start | 2月25日(水) 申込締切日:2/13 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 開催中止 | Versal Adaptive SoC | 2026年2月 | 202602131700 | 0 |

| AdovancedMin2.png | Embedded Heterogeneous Design | 2月26日(木)-27日(金) 申込締切日:2/16 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | Versal Adaptive SoC | 2026年2月 | 202602161700 | 0 |

| Vivado.png | デザイン クロージャ テクニック デザイン&パワー | 3月3日(火) 申込締切日:2/19 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 開催中止 | FPGAとVivadoツール | 2026年3月 | 202602191700 | 0 |

| AdovancedMin2.png | Versal AI Engine 1: アーキテクチャとデザインフロー | 3月3日(火)-4日(水) 申込締切日:2/19 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | Versal Adaptive SoC | 2026年3月 | 202602191700 | 0 |

| eembe.png | Embedded Systems Software Design Basic | 3月3日(火)-4日(水) 申込締切日:2/19 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 開催中止 | SoCとVitisツール | 2026年3月 | 202602191700 | 0 |

| eembe.png | Embedded Systems Software Design OS | 3月5日(木) 申込締切日:2/24 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2193 | SoCとVitisツール | 2026年3月 | 202602241700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC:アーキテクチャ | 3月5日(木)-6日(金) 申込締切日:2/24 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | Versal Adaptive SoC | 2026年3月 | 202602241700 | 0 |

| Vivado.png | Vivado Design Suite を使用したArtix-7 FPGA設計・開発入門 | 3月6日(金) 申込締切日:2/25 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2195 | FPGAとVivadoツール | 2026年3月 | 202602251700 | 1 |

| Vivado.png | Vivado ロジック解析を使用したデバッグ 基礎編 | 3月10日(火) 申込締切日:2/27 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2196 | FPGAとVivadoツール | 2026年3月 | 202602271700 | 1 |

| eembe.png | Migrating to the Vitis Unified IDE | 3月11日(水) 申込締切日:3/2 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2197 | SoCとVitisツール | 2026年3月 | 202603021700 | 1 |

| embe.png | OS and Hypervisors in Adaptive SoCs | 3月12日(木)-13日(金) 申込締切日:3/3 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 2198 | MPSoC/SoM | 2026年3月 | 202603031700 | 1 |

| Vivado.png | タイミングクロージャテクニックPart1 | 3月12日(木) 申込締切日:3/3 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2199 | FPGAとVivadoツール | 2026年3月 | 202603031700 | 1 |

| Vivado.png | タイミングクロージャテクニックPart2 | 3月13日(金) 申込締切日:3/4 10:00~17:30 | オンライン TC:6TC 現金:¥66,000 | 2200 | FPGAとVivadoツール | 2026年3月 | 202603041700 | 1 |

| lang.png | Verification with SystemVerilog | 3月16日(月)-17日(火) 申込締切日:3/5 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2201 | HDL言語と検証 | 2026年3月 | 202603051700 | 1 |

| eembe.png | Zynq SoC エンベデッドシステム開発 | 3月16日(月)-17日(火) 申込締切日:3/5 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2202 | SoCとVitisツール | 2026年3月 | 202603051700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 3月18日(水)-19日(木) 申込締切日:3/9 10:00~17:30 | 新横浜(hdLab) TC:8TC 現金:¥107,800 | 2203 | FPGAとVivadoツール | 2026年3月 | 202603091700 | 1 |

| lang.png | [VHDL] Xilinx/Vivadoツールを使ったRTL設計初級 | 3月18日(水)-19日(木) 申込締切日:3/9 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2204 | HDL言語と検証 | 2026年3月 | 202603091700 | 1 |

| eembe.png | ソフト&ハード設計実装セミナー | 3月23日(月) 申込締切日:3/11 10:00~17:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2205 | SoCとVitisツール | 2026年3月 | 202603111700 | 1 |

| embe.png | Kria KV260 入門 | 3月24日(火) 申込締切日:3/12 13:00~18:00 | 新横浜(hdLab) TC:8TC 現金:TCのみ | 2206 | MPSoC/SoM | 2026年3月 | 202603121700 | 1 |

| AdovancedMin2.png | Versal adaptive SoC:デザインメソドロジーPart1 | 3月24日(火)-25日(水) 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 開催中止 | Versal Adaptive SoC | 2026年3月 | 202603121700 | 0 |

| AdovancedMin2.png | Versal adaptive SoC:デザインメソドロジーPart2 | 3月26日(木) 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 開催中止 | Versal Adaptive SoC | 2026年3月 | 202603161700 | 0 |

| AdovancedMin2.png | Versal Adaptive SoC:ネットワーク オン チップ | 3月27日(金) 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 開催中止 | Versal Adaptive SoC | 2026年3月 | 202603171700 | 0 |

| embe.png | Zynq UltraScale+ MPSoC Boot and Platform Management | 3月30日(月)-31日(火) 申込締切日:3/18 10:00~18:00 | 新横浜(hdLab) TC:12TC 現金:¥132,000 | 2210 | MPSoC/SoM | 2026年3月 | 202603181700 | 1 |

| Vivado.png | Vivado Design Suite を使用したArtix-7 FPGA設計・開発入門 | 4月7日(火) 申込締切日:3/27 10:00~17:30 | 新横浜(hdLab) TC:4TC 現金:¥53,900 | 2212 | FPGAとVivadoツール | 2026年4月 | 202603271700 | 1 |

| lang.png | [Verilog] Xilinx/Vivadoツールを使ったRTL設計初級 | 4月7日(火)-8日(水) 申込締切日:3/27 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2213 | HDL言語と検証 | 2026年4月 | 202603271700 | 1 |

| Vivado.png | Vivado Design Suite でのUltraFast設計手法 | 4月9日(木) 申込締切日:3/31 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2214 | FPGAとVivadoツール | 2026年4月 | 202603311700 | 1 |

| eembe.png | Vitis HLSを使った高位合成 | 4月9日(木)-10日(金) 申込締切日:3/31 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2215 | SoCとVitisツール | 2026年4月 | 202603311700 | 1 |

| eembe.png | Zynq SoC システムアーキテクチャ | 4月14日(火)-15日(水) 申込締切日:4/3 10:00~18:00 | オンライン TC:8TC 現金:¥107,800 | 2216 | SoCとVitisツール | 2026年4月 | 202604031700 | 1 |

| eembe.png | ARTYを使用したMicroBlaze-v開発入門 | 4月15日(水) 申込締切日:4/6 10:00~18:00 | 新横浜(hdLab) TC:6TC 現金:¥66,000 | 2217 | SoCとVitisツール | 2026年4月 | 202604061700 | 1 |

| Vivado.png | Vivado Design Suite でのインプリメント手法 | 4月16日(木) 申込締切日:4/7 10:00~17:30 | オンライン TC:4TC 現金:¥53,900 | 2218 | FPGAとVivadoツール | 2026年4月 | 202604071700 | 1 |

| Vivado.png | Vivado Design Suite でのFPGA設計導入 | 4月20日(月)-21日(火) 申込締切日:4/9 10:00~17:30 | オンライン TC:8TC 現金:¥107,800 | 2219 | FPGAとVivadoツール | 2026年4月 | 202604091700 | 1 |

| eembe.png | Yoctoを使用した組み込みLinux開発 | 4月22日(水) 申込締切日:4/13 10:00~18:00 | オンライン TC:6TC 現金:¥66,000 | 2220 | SoCとVitisツール | 2026年4月 | 202604131700 | 1 |

| embe.png | Zynq UltraScale+ MPSoC システムアーキテクチャ | 4月23日(木)-24日(金) 申込締切日:4/14 10:00~18:00 | オンライン TC:12TC 現金:¥132,000 | 2221 | MPSoC/SoM | 2026年4月 | 202604141700 | 1 |

| lang.png | FPGA向けRTL設計スタイルガイドセミナー | 4月23日(木)-24日(金) 申込締切日:4/14 10:00~18:00 | 新横浜(hdLab) TC:8TC 現金:¥107,800 | 2222 | HDL言語と検証 | 2026年4月 | 202604141700 | 1 |

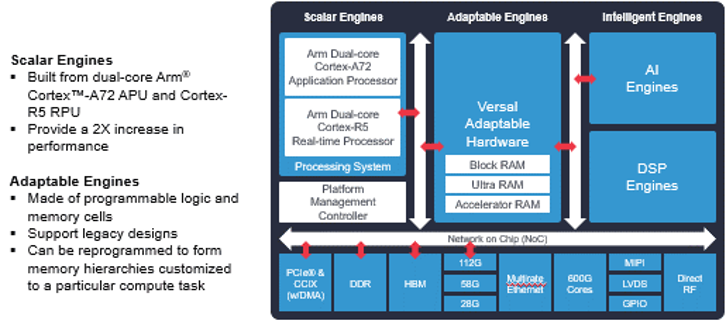

本コースでは、Adaptable Engine、高速 I/O、クロッキング、Scalar Engine、Intelligent Engine、プログラマブル ネットワーク オン チップ (NoC) など、AMD Versal™ Adaptive SoC アーキテクチャのビルディング ブロックについて学びます。 また、最先端のメモリおよびインターフェイス テクノロジを使用して、あらゆるアプリケーションに強力な異種混合アクセラレーションを提供する方法についても学びます。

このコースの重点項目は次のとおりです。

▪ VersalアダプティブSoCのアーキテクチャの説明

▪ Versal アーキテクチャで利用可能なさまざまなエンジンと、それらのエンジンに含まれるリソースの説明

▪ ネットワークオンチップ(NoC)とAIエンジンのアーキテクチャの説明

▪ Versal アダプティブ SoC で利用可能なメモリ ソリューションとプログラミング インターフェイスの概要

▪ Versal アダプティブ SoC で利用可能な PCI Express® およびシリアル トランシーバー ソリューションの特定

【ご注意下さい】

このコースの説明は日本語で行いますが、テキストは英語となります。

従来の「Versal ACAP: アーキテクチャとメソドロジー1、2」は「アーキテクチャ」と「デザインメソドロジー」に分割されました。

| コース名 | Versal Adaptive SoC:アーキテクチャ |

|---|---|

| ソフトウェアツール | ・Vivado ML Edition 2023.1 ・Vitis unified software platform 2023.1 |

| ハードウェア | ・Architecture: Versal adaptive SoC ・Demo board: Versal VCK190 Evaluation Platform |

| トレーニング期間 | 2日間 |

| 受講料 | 1名様 12TC or 132,000円(税込) |

| 受講対象者 | ハードウエアエンジニア、ソフトウエアエンジニア、システムアーキテクト、DSPユーザー および Vesal Adaptive SoCデバイスの設計手法を学びたい方 |

| 受講要件 | ・AMD FPGA およびアダプティブ SoC に関する基礎知識 ・Vivado™ および Vitis™ ツールの基本的な知識 |

| コース内容 | ※テキストは全て英語です! Day 1 ・Introduction Describes the need for Versal devices and offers an overview of the Versal portfolio. {Lecture} ・Architecture Overview Provides a high-level overview of the Versal architecture, illustrating the various engines available in the Versal architecture. {Lecture} ・Design Tool Flow Maps the various engines in the Versal architecture to the tools required and describes how to target them for final image assembly. {Lecture, Lab} ・Adaptable Engines (PL) Describes the logic resources available in the Adaptable Engine. {Lecture} ・SelectIO Resources Describes the I/O bank, SelectIO™ interface, and I/O delay features. {Lecture} ・Clocking Architecture Discusses the clocking architecture, clock buffers, clock routing, clock management functions, and clock de-skew. {Lecture, Lab} ・Processing System Reviews the ArmR CortexR-A72 processor APU and Cortex-R5 processor RPU that form the Scalar Engine. The platform management controller (PMC), processing system manager (PSM), I/O peripherals, and PS-PL interfaces are also covered. {Lecture} ・PMC and Boot and Configuration Describes the platform management controller, platform loader and manager (PLM) software and boot and configuration. {Lecture, Lab} ・System Interrupts Discusses the different system interrupts and interrupt controllers. {Lecture} Day 2 ・Timers, Counters, and RTC Provides an overview of timers and counters, including the system counter, triple timer counter (TTC), watchdog timer, and real-time clock (RTC). {Lecture} ・DSP Engine Describes the DSP58 slice and compares the DSP58 slice with the DSP48 slice. DSP58 modes are also covered in detail. {Lecture, Lab} ・AI Engine Discusses the AI Engine array architecture, terminology, and AIE interfaces. {Lecture, Lab} ・NoC Introduction and Concepts Covers the reasons to use the network on chip, its basic elements, and common terminology. {Lecture, Lab} ・Memory Solutions Describes the available memory resources, such as block RAM, UltraRAM, LUTRAM, embedded memory, OCM, and DDR. The integrated memory controllers are also covered. {Lecture} ・Programming Interfaces Reviews the various programming interfaces in the Versal device. {Lecture} ・PCI Express & CCIX Provides an overview of the CCIX PCIe module and describes the PL and CPM PCIe blocks. {Lecture, Lab} ・Serial Transceivers Describes the transceivers in the Versal device. {Lecture} ・System Migration Compares the various functional blocks of the Versal devices to previous-generation devices. Describes the migration of designs from the UltraScale™ and UltraScale+™ architectures to the Versal architecture. {Lecture} |